hello TI E2E

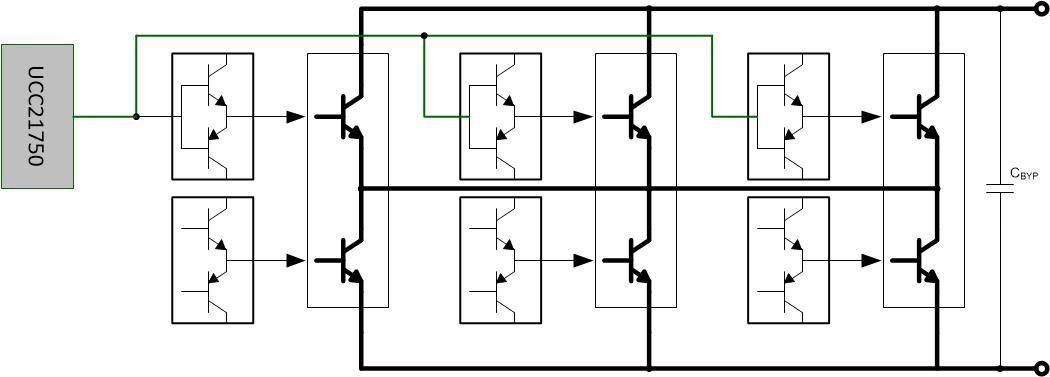

I have three big IGBT modules in parallel that are physically placed about 2 inches apart, because the size of IGBT modules are large.

Each IGBT modules has two IGBTs in half-bridge configuration. And each IGBT has its own local BJT buffer.

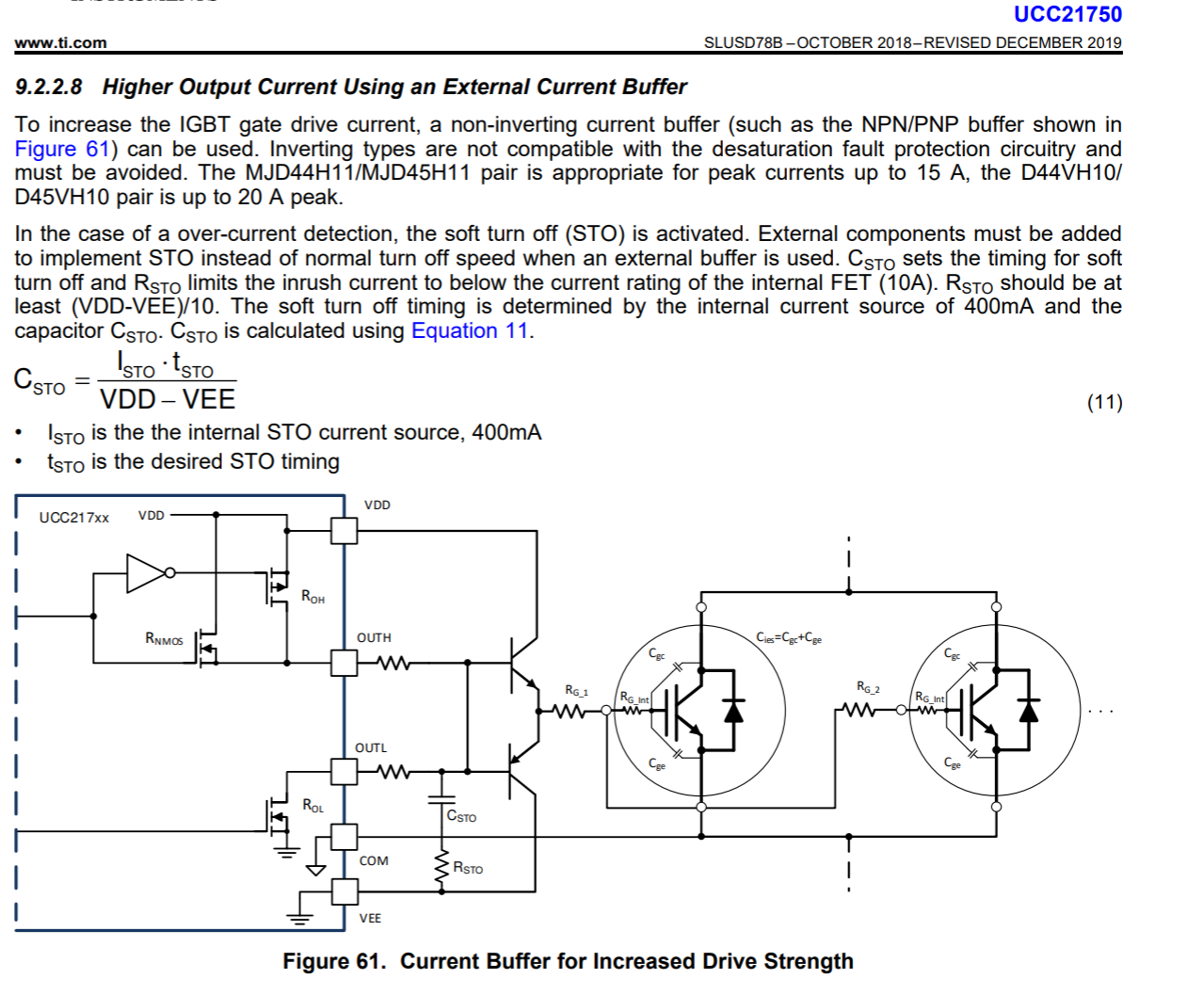

I have a question about the external R and C for soft turn off (STO). that are shown in Fig. 61 on page 45 in the datasheet.

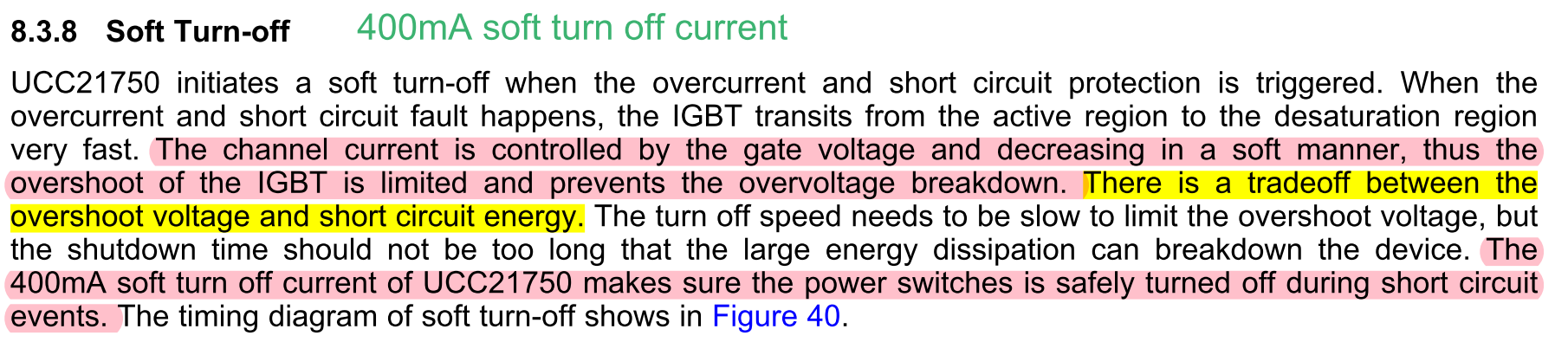

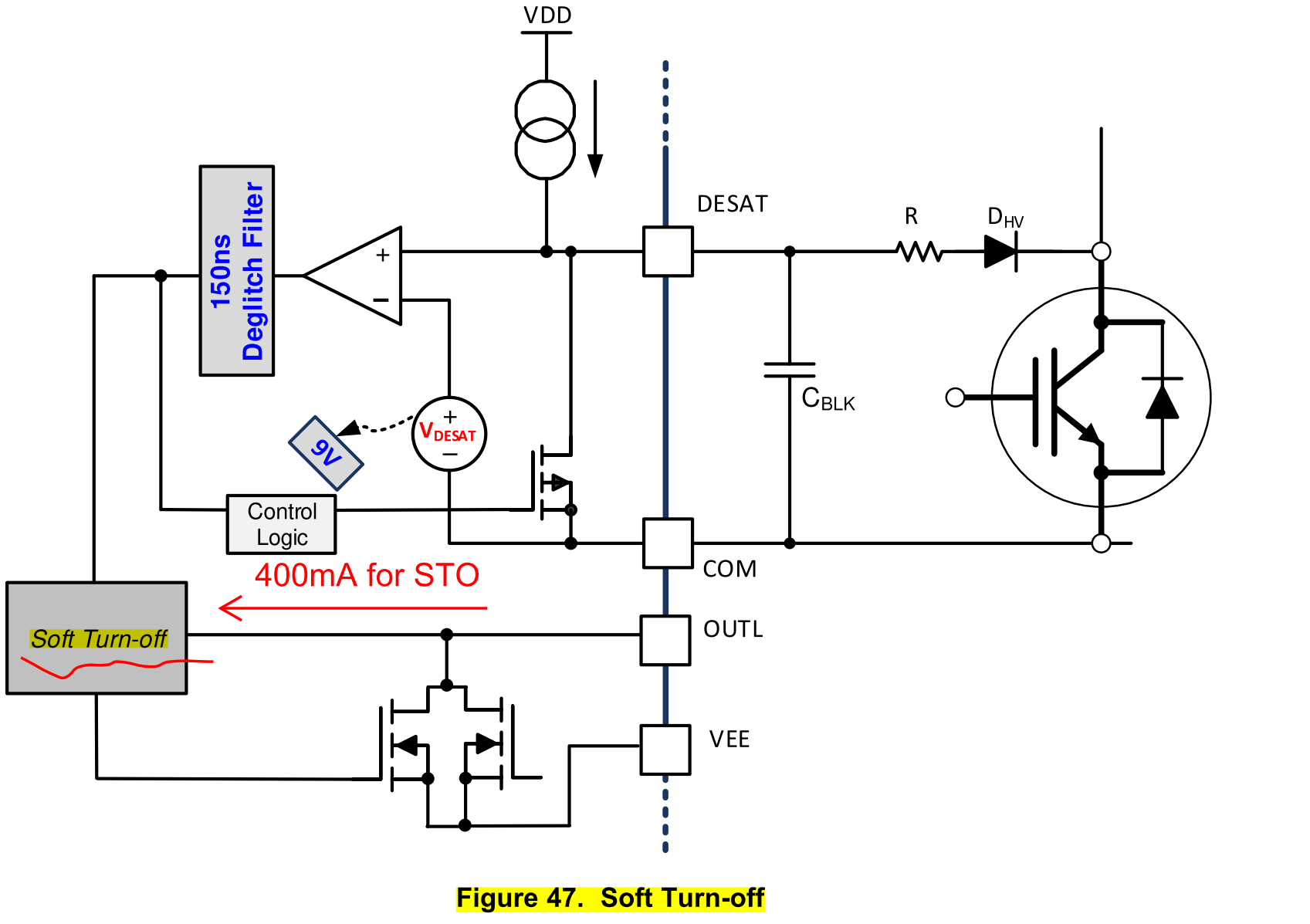

I attached a few captures from datasheet here for easy communication.

Q1: Shall I put a single pair of RC close to UCC21750 to soft turn off all IGBTs' BJT buffers? OR I should put distributed parallel pairs of RC (reduced value by # of pairs) close to each BJT buffer as close as possible.

The reason I am asking is that I found some Vge ringing during STO which is triggered by Desat fault. The debugging is still in progress. I didn't post any oscilloscope capture here yet.

Q2: What are the purposes of the two back-to-back MOSFETs for in Fig.47 on page 31? Could you explain it to me?

Any insights into external RC for STO will be much appreciated.

Thank you.

YZ