Other Parts Discussed in Thread: LM7480, LM74800-Q1

Hi,

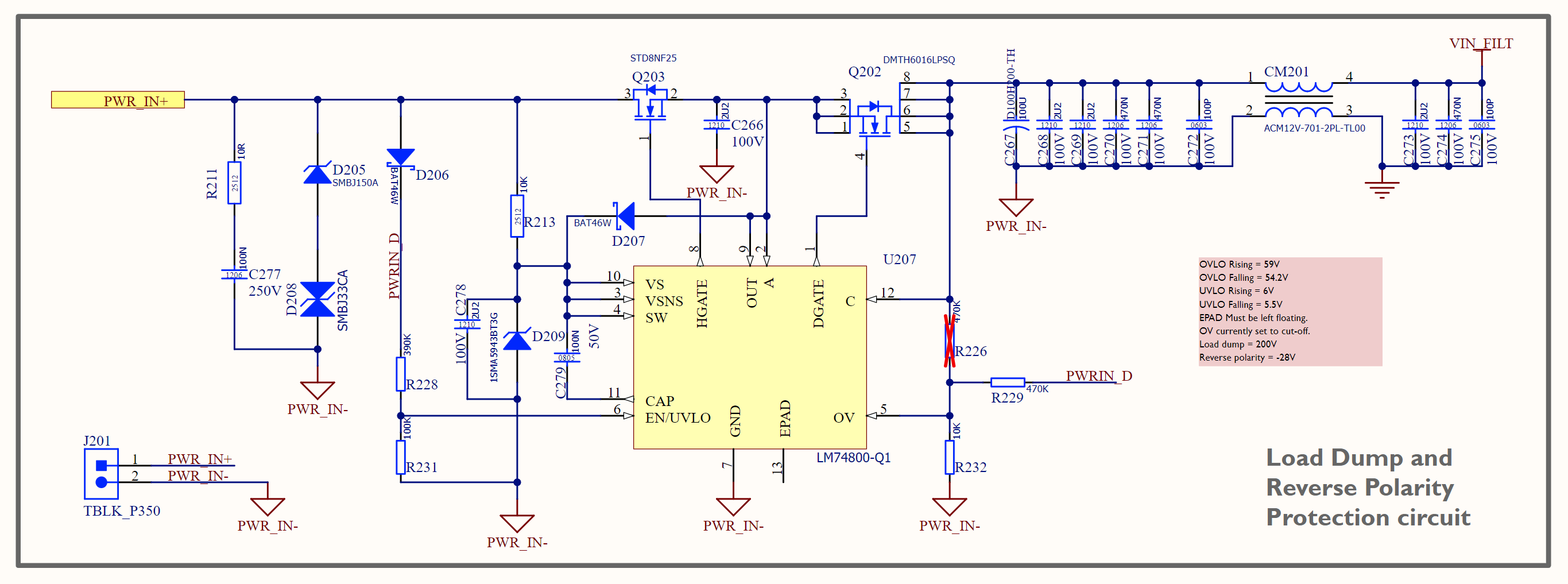

I am planning on using the LM7480-Q1 for a device that can work on automotive 12V rail, 24V rail and 48V rail.

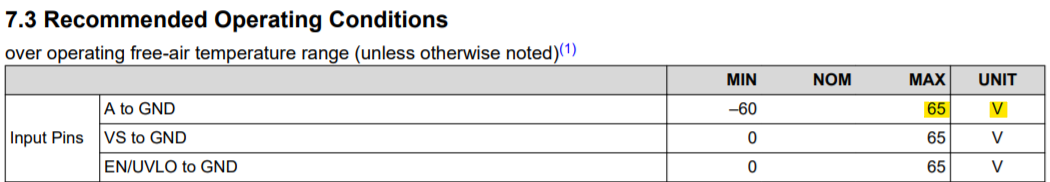

If I combine the requirements for ISO16750 and ISO21780, I have a wide input voltage range = 6V to 58V, in which I need to pass with ClassA rating.

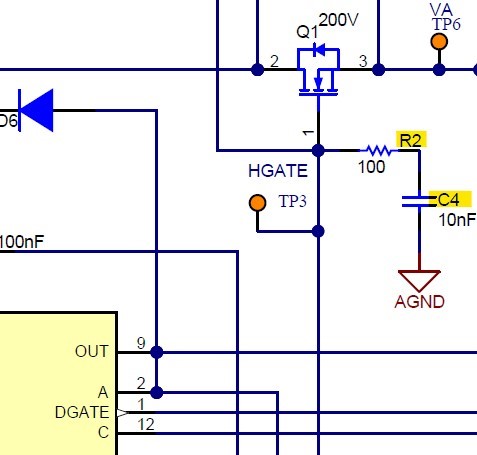

Is it possible to set the LM7480-Q1 to work at this voltage range? i.e. UVLO set to 6V, OV set to 58V? Can I connect in common-source topology as described in 9.5.2 of datasheet

Datasheet link: https://www.ti.com/lit/gpn/lm7480-q1

This means that voltage at HGATE and DGATE (with respect to GND) must be greater than voltage at A and OUT, i.e. >58V. Is this possible? What is the max rating of the charge pump output?

If this is not possible could you please suggest another part that can work with all three 12V, 24V and 48V rails and help suppress load dumps, reverse polarity and transients?

Thanks in advance

Navin