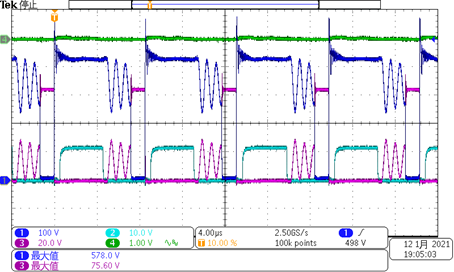

Our customer found folloing SR timing delay waveform. (delay time: about 550ns)

<Condition>

IN:DC240V-DC340V

OUT:13.5V/4A

Also they didn't found low Vin and light load condition.

CH1:Primary FET_VDS

CH2:Secondary FET_VGS

CH3:Secondary FET_VDS

CH4:Vout (AC mode)

Fsw:116kHz

Primary FET ON time:1.35us

Please let us know why these waveform is found.

They think these waveform have an impact on efficiency.

If you need any other information,please let us know it.

Regards,