Other Parts Discussed in Thread: CSD95490Q5MC,

Hi,

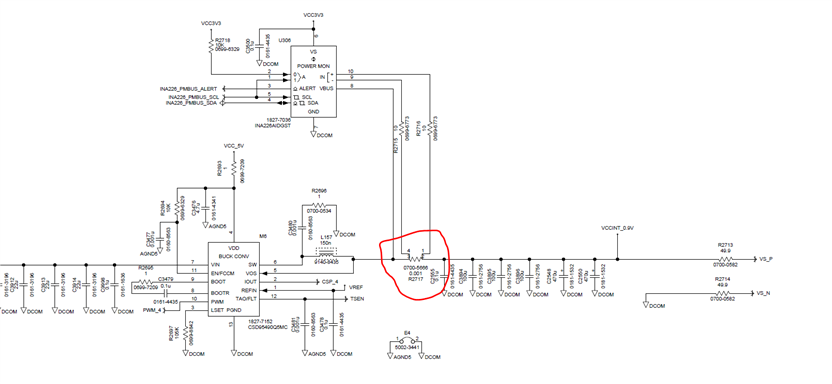

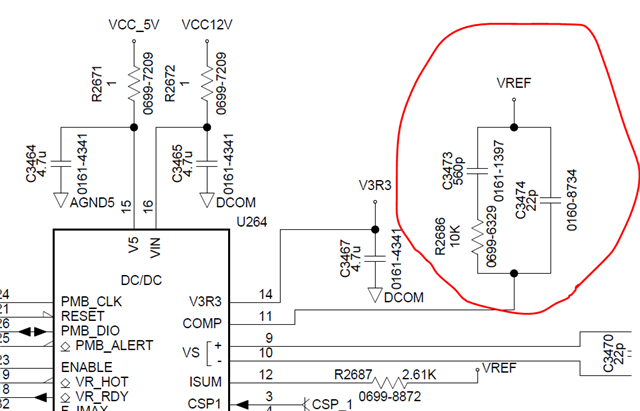

We have completed a design with TPS53647 and 4 Power Stages- CSD95490Q5MC for 0.9V output at 125A.

We will be using TPS53647 in pin strapping mode.

In the datasheet, at page 9 the maximum Imax value is 120A. But in our design we require 125A continuous current. So is it possible to draw 125A current from the output with Imax value set to 120A without triggering the OCP event.

Also, please review the attached schematic for our output requirements.

Please check the pin strap values and also the IMON circuitry and compensation components values for the output requirements.

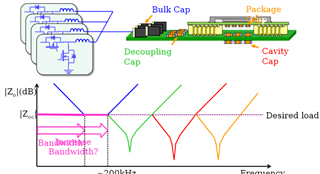

And one more thing, TPS53647 running at 500Khz and we are using 470uF cap with part no. EEFGX0D471R at the output as this part no. is suggested in the webench simulation also. But when we look at the capacitance vs frequency graph of EEFGX0D471R, we see that at 500kHz the graph doesn't show any capacitance value at 500KHz as shown below:

Do we need to choose some other part no. for the output cap and if yes, why it is used in Webench simulation? Please also verify the input and output caps value and quantity.

Thanks,

Lalit