Other Parts Discussed in Thread: PTD08D210W, PTD08A020W, , UCD7242

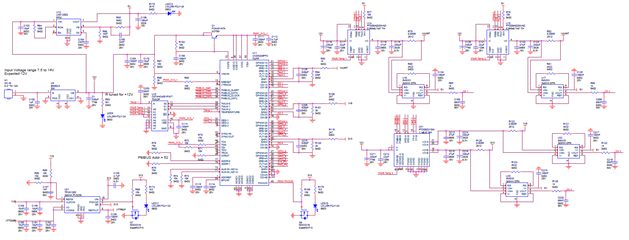

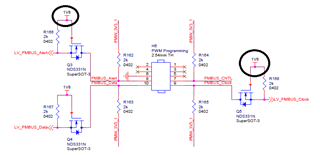

I have a system with 2 x UCD9248's controlling a number of power modules, PTD08A020W's & PTD08D210W's.

The first rail to be sequenced I set to have an on delay of 500 ms then to have a rise time of 50 ms, this is driving the PTD08A020W's.

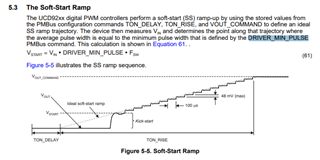

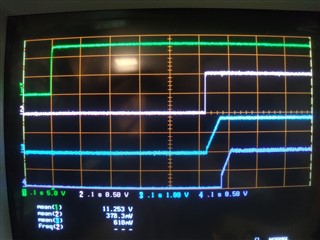

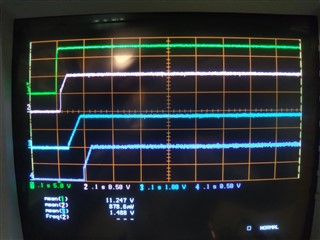

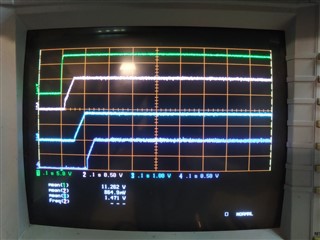

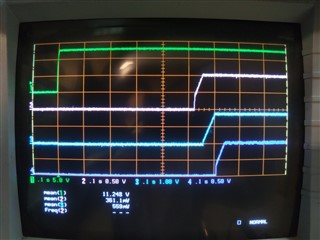

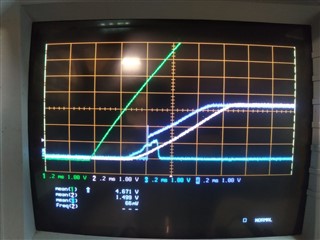

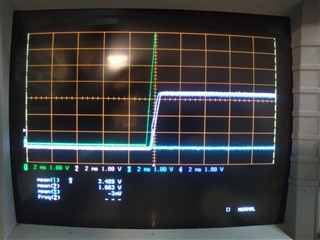

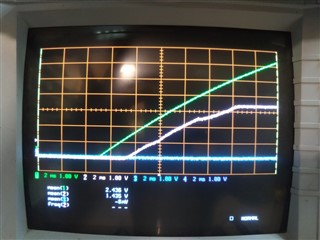

When checking on a scope I see the correct on delay but the rise time is almost immediate, if however I turn the on delay to 0 ms, I see no delay and a correct rise time. I tried leaving the on delay at 500 ms and setting the rise time to 550 ms, and what I see is nothing for 500 ms then a big jump up to nearly full scale, then 50 ms of a very slow ramp, as if its been ramping from 0 ms with the aim of completing at 550 ms.

It looks like the ramp is applied from T 0 at whatever you set the rise time, and then the output is just gated with on delay, so if its already ramped up its just straight on. I don't think that is what is intended by the settings is that expected behaviour?

The second issue I'm having is related to this issue (+) PTD08D210W: FLT flag being set from power on - Power management forum - Power management - TI E2E support forums whereby I am seeing one module have its FLT flag set from power up, this is causing my sequencer to immediately abort sequencing and shut down. Looking in Advanced options -> driver config, it is set to ignore FLT state on start & restart, which I would expect t stop this problem, but it doesn't, any idea why the setting appears to have no effect?

Thanks,

Bryn

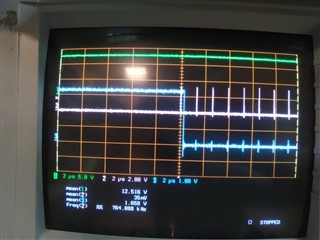

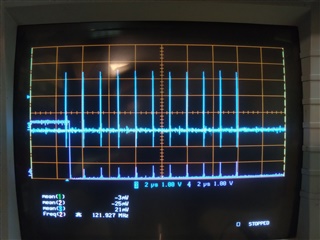

Ton = 500 ms, Driver Min Pulse = 140 ns.

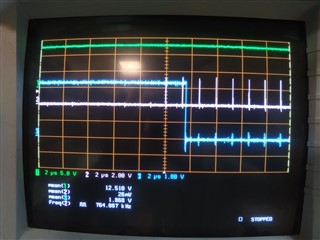

Ton = 500 ms, Driver Min Pulse = 140 ns. Ton = 0 ms, Driver Min Pulse = 140 ns.

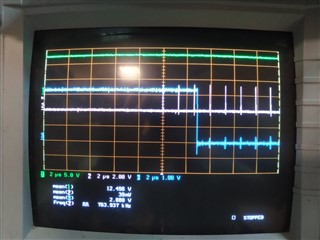

Ton = 0 ms, Driver Min Pulse = 140 ns. Ton = 0 ms, Driver Min Pulse = 70 ns.

Ton = 0 ms, Driver Min Pulse = 70 ns. Ton = 500 ms, Driver Min Pulse = 70 ns.

Ton = 500 ms, Driver Min Pulse = 70 ns.

- Fast ramp 12V PSU - 0.2 ms per div

- Fast ramp 12V PSU - 0.2 ms per div - Fast ramp 12V PSU - 2 ms per div

- Fast ramp 12V PSU - 2 ms per div - Slow ramp 12V PSU - 2 ms per div

- Slow ramp 12V PSU - 2 ms per div