My last thread:

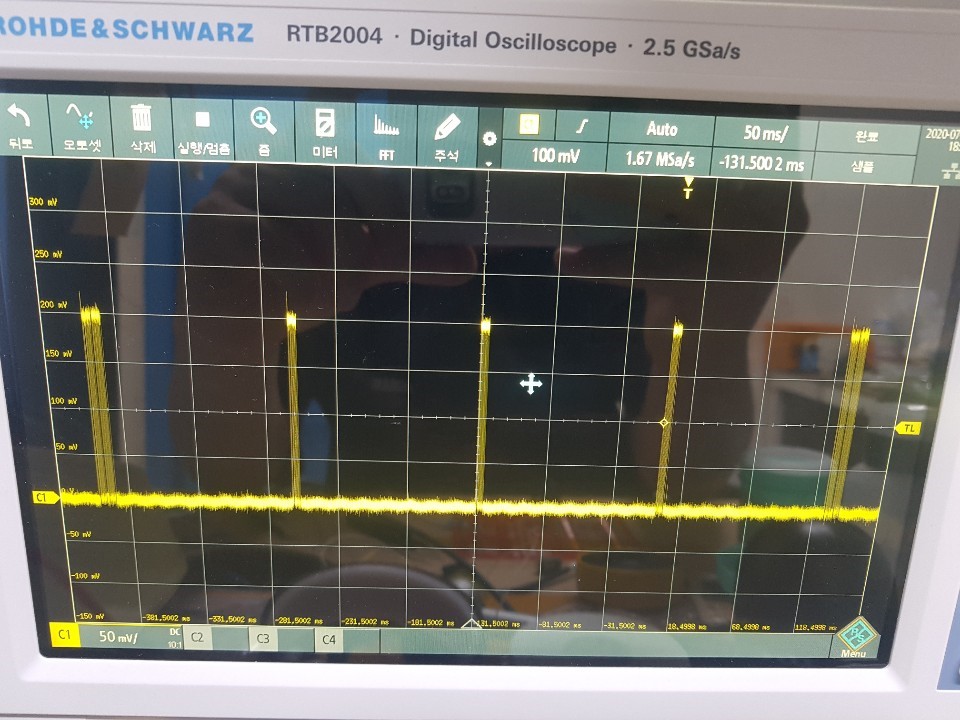

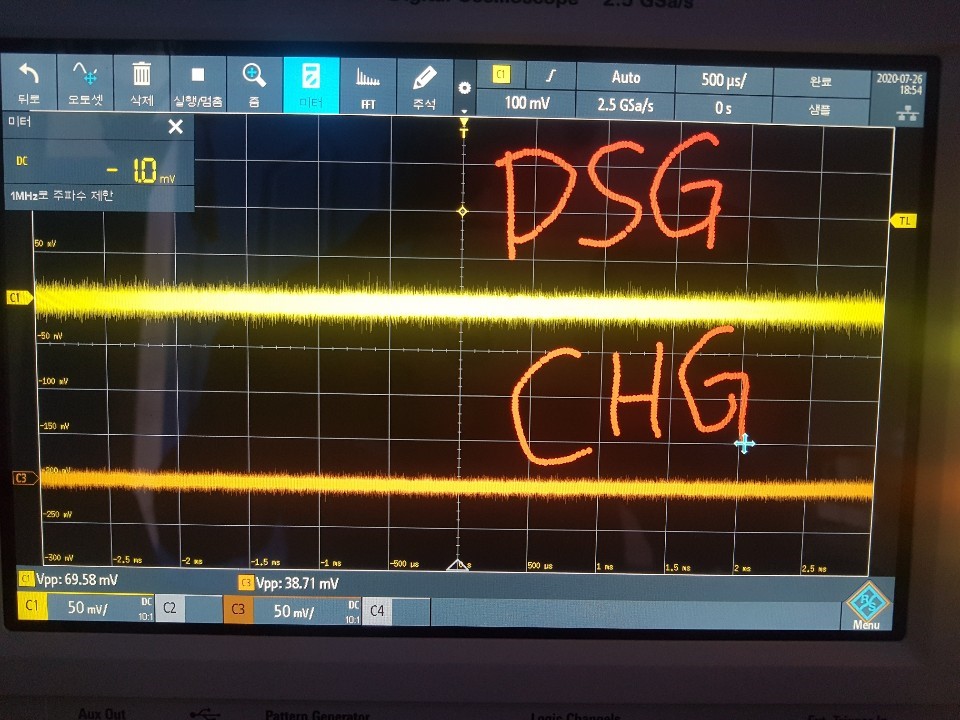

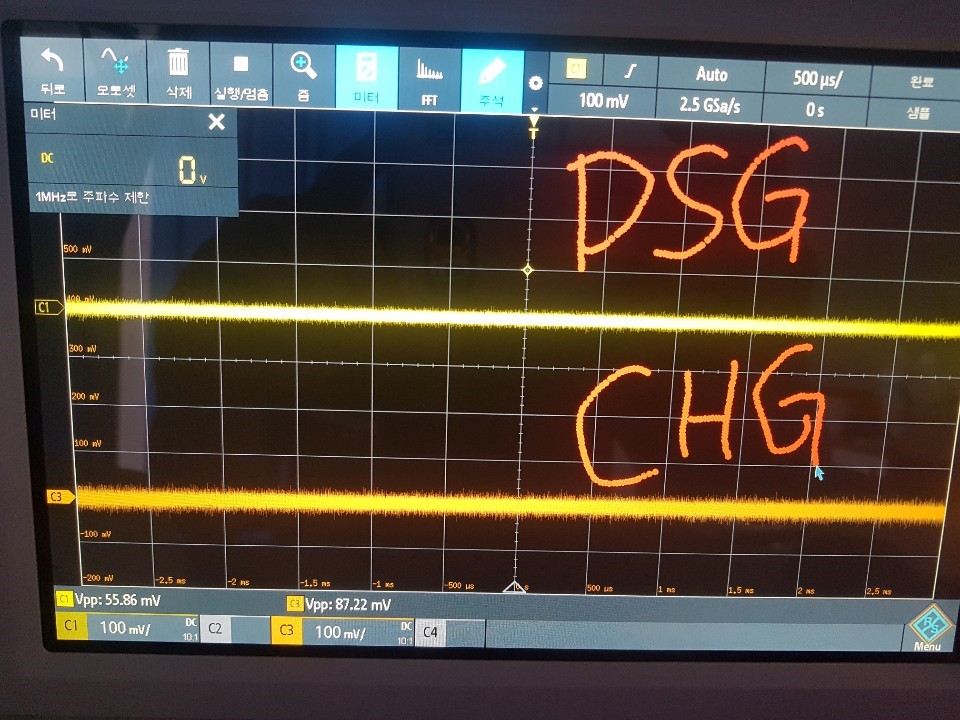

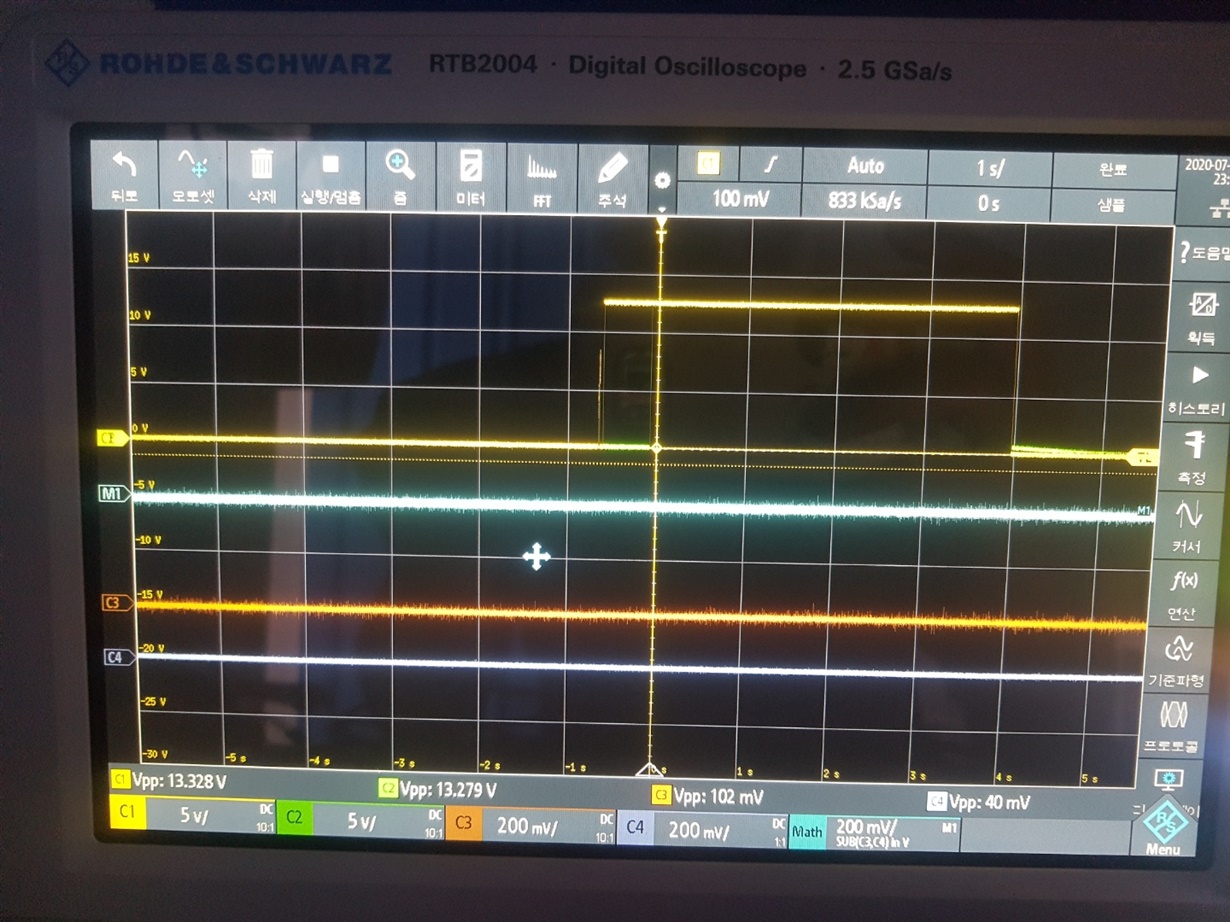

I tried to fix my circuit with my equipment, PSU, and Oscilloscope.

I supply 18V via PSU with 200Ohm Resistor each one to 5S.

Also, I make circuits for Disable Hibernate mode and CTRD, CTRC for ground.

And I used OCDP resistor 100Kohm for using the EEPROM setting.

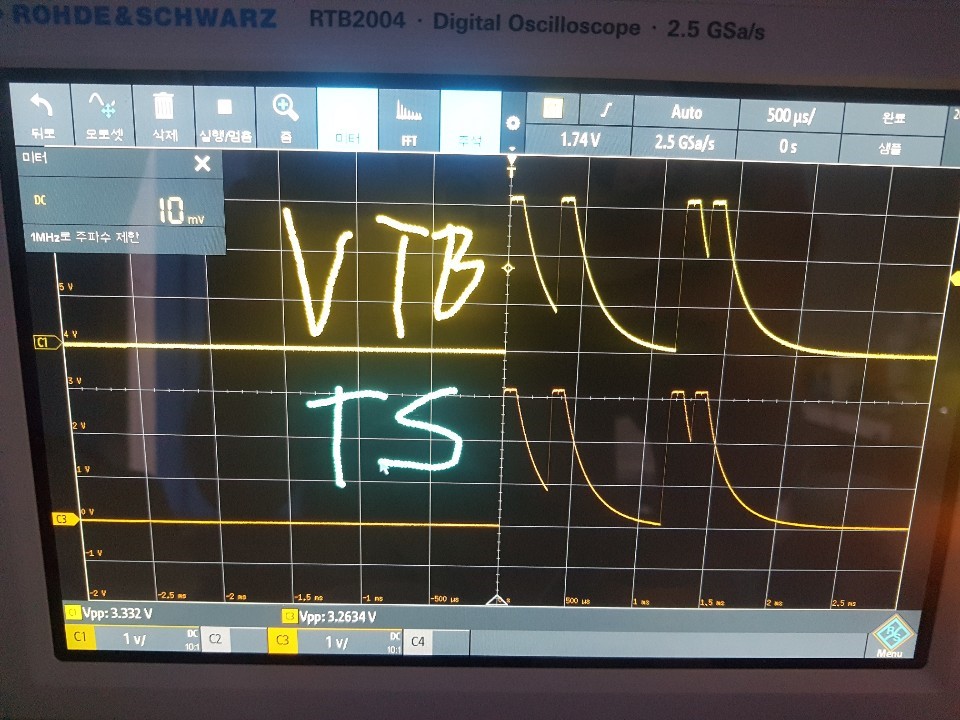

But I can't get Voltage 18V via P- and C5.

I can get only around 16V on P- and FETs' Drain voltage between C5 and Drain 1.6V~3V.

RSNS : 0.002R 1% 3920

MOSFET : FDBL86066-F085(CHG and DSG each 2pcs)