Part Number: AM623

Other Parts Discussed in Thread: TAC5111

Tool/software:

hi

when configure am623 MCASP2 as i2s master , I use the following record command ,it will report error. please help check why

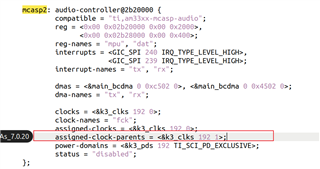

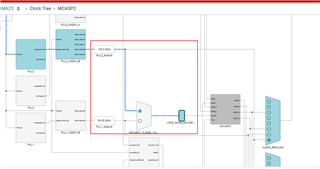

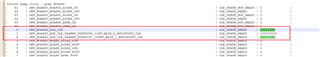

Warning: rate is not accurate (requested = 48000Hz, got = 44100H[ 598.784554] davinci-mcasp 2b20000.audio-controller: Too fast reference clock (96000000)

z)

please, try the plug plugin

[ 598.793924] davinci-mcasp 2b20000.audio-controller: Sample-rate is off by 400 PPM

best regards