Part Number: AM623

Other Parts Discussed in Thread: TLV320AIC3101

Hi, TI expert!

I have a development environment for am6234, with our own evaluation board.

The evaluation board has a tlv320aic3101 audio codec chip.

The software SDK version is PROCESSOR-SDK-LINUX-RT-AM62X-08.06.00.42.

We attempted to use the mcasp of am6234 as the master device and the tlv320aic3101 codec chip as the slave device in I2S mode to record and playback a sound.

The experimental result is that we are able to record the sound, but when we play back the recorded sound, it sounds like it is playing at double speed, similar to watching a TV show on fast forward.

I made the following modifications to the SDK:

Modification 1: Add audio_refclk related code in the syscon-clk.c file

diff --git a/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/drivers/clk/keystone/syscon-clk.c b/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/drivers/clk/keystone/syscon-clk.c

index 7da6fa1..109d3f1 100755

--- a/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/drivers/clk/keystone/syscon-clk.c

+++ b/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/drivers/clk/keystone/syscon-clk.c

@@ -4,10 +4,12 @@

*/

#include <linux/clk-provider.h>

+#include <linux/kernel.h>

#include <linux/mfd/syscon.h>

#include <linux/module.h>

#include <linux/platform_device.h>

#include <linux/regmap.h>

+#include <linux/slab.h>

struct ti_syscon_gate_clk_priv {

struct clk_hw hw;

@@ -61,21 +63,31 @@ static const struct clk_ops ti_syscon_gate_clk_ops = {

static struct clk_hw

*ti_syscon_gate_clk_register(struct device *dev, struct regmap *regmap,

+ const char *parent_name,

const struct ti_syscon_gate_clk_data *data)

{

struct ti_syscon_gate_clk_priv *priv;

struct clk_init_data init;

+ char *name = NULL;

int ret;

priv = devm_kzalloc(dev, sizeof(*priv), GFP_KERNEL);

if (!priv)

return ERR_PTR(-ENOMEM);

- init.name = data->name;

init.ops = &ti_syscon_gate_clk_ops;

- init.parent_names = NULL;

- init.num_parents = 0;

- init.flags = 0;

+ if (parent_name) {

+ name = kasprintf(GFP_KERNEL, "%s:%s", data->name, parent_name);

+ init.name = name;

+ init.parent_names = &parent_name;

+ init.num_parents = 1;

+ init.flags = CLK_SET_RATE_PARENT;

+ } else {

+ init.name = data->name;

+ init.parent_names = NULL;

+ init.num_parents = 0;

+ init.flags = 0;

+ }

priv->regmap = regmap;

priv->reg = data->offset;

@@ -83,6 +95,10 @@ static struct clk_hw

priv->hw.init = &init;

ret = devm_clk_hw_register(dev, &priv->hw);

+

+ if (name)

+ kfree(init.name);

+

if (ret)

return ERR_PTR(ret);

@@ -94,25 +110,30 @@ static int ti_syscon_gate_clk_probe(struct platform_device *pdev)

const struct ti_syscon_gate_clk_data *data, *p;

struct clk_hw_onecell_data *hw_data;

struct device *dev = &pdev->dev;

+ int num_clks, num_parents, i;

+ const char *parent_name;

struct regmap *regmap;

- int num_clks, i;

data = device_get_match_data(dev);

if (!data)

return -EINVAL;

- regmap = syscon_node_to_regmap(dev->of_node);

- if (IS_ERR(regmap)) {

- if (PTR_ERR(regmap) == -EPROBE_DEFER)

- return -EPROBE_DEFER;

- dev_err(dev, "failed to find parent regmap\n");

- return PTR_ERR(regmap);

- }

+ regmap = device_node_to_regmap(dev->of_node);

+ if (IS_ERR(regmap))

+ return dev_err_probe(dev, PTR_ERR(regmap),

+ "failed to get regmap\n");

num_clks = 0;

for (p = data; p->name; p++)

num_clks++;

+ num_parents = of_clk_get_parent_count(dev->of_node);

+ if (of_device_is_compatible(dev->of_node, "ti,am62-audio-refclk") &&

+ num_parents == 0) {

+ return dev_err_probe(dev, -EINVAL,

+ "must specify a parent clock\n");

+ }

+

hw_data = devm_kzalloc(dev, struct_size(hw_data, hws, num_clks),

GFP_KERNEL);

if (!hw_data)

@@ -120,16 +141,23 @@ static int ti_syscon_gate_clk_probe(struct platform_device *pdev)

hw_data->num = num_clks;

+ parent_name = of_clk_get_parent_name(dev->of_node, 0);

for (i = 0; i < num_clks; i++) {

hw_data->hws[i] = ti_syscon_gate_clk_register(dev, regmap,

+ parent_name,

&data[i]);

if (IS_ERR(hw_data->hws[i]))

dev_warn(dev, "failed to register %s\n",

data[i].name);

}

- return devm_of_clk_add_hw_provider(dev, of_clk_hw_onecell_get,

- hw_data);

+ if (num_clks == 1)

+ return devm_of_clk_add_hw_provider(dev, of_clk_hw_simple_get,

+ hw_data->hws[0]);

+ else

+ return devm_of_clk_add_hw_provider(dev, of_clk_hw_onecell_get,

+ hw_data);

+

}

#define TI_SYSCON_CLK_GATE(_name, _offset, _bit_idx) \

@@ -169,6 +197,11 @@ static const struct ti_syscon_gate_clk_data am62_clk_data[] = {

{ /* Sentinel */ },

};

+static const struct ti_syscon_gate_clk_data am62_audio_clk_data[] = {

+ TI_SYSCON_CLK_GATE("audio_refclk", 0x0, 15),

+ { /* Sentinel */ },

+};

+

static const struct of_device_id ti_syscon_gate_clk_ids[] = {

{

.compatible = "ti,am654-ehrpwm-tbclk",

@@ -182,6 +215,10 @@ static const struct of_device_id ti_syscon_gate_clk_ids[] = {

.compatible = "ti,am62-epwm-tbclk",

.data = &am62_clk_data,

},

+ {

+ .compatible = "ti,am62-audio-refclk",

+ .data = &am62_audio_clk_data,

+ },

{ }

};

MODULE_DEVICE_TABLE(of, ti_syscon_gate_clk_ids);

The complete modified code is as follows:

// SPDX-License-Identifier: GPL-2.0

/*

* Copyright (C) 2020 Texas Instruments Incorporated - https://www.ti.com/

*/

#include <linux/clk-provider.h>

#include <linux/kernel.h>

#include <linux/mfd/syscon.h>

#include <linux/module.h>

#include <linux/platform_device.h>

#include <linux/regmap.h>

#include <linux/slab.h>

struct ti_syscon_gate_clk_priv {

struct clk_hw hw;

struct regmap *regmap;

u32 reg;

u32 idx;

};

struct ti_syscon_gate_clk_data {

char *name;

u32 offset;

u32 bit_idx;

};

static struct

ti_syscon_gate_clk_priv *to_ti_syscon_gate_clk_priv(struct clk_hw *hw)

{

return container_of(hw, struct ti_syscon_gate_clk_priv, hw);

}

static int ti_syscon_gate_clk_enable(struct clk_hw *hw)

{

struct ti_syscon_gate_clk_priv *priv = to_ti_syscon_gate_clk_priv(hw);

return regmap_write_bits(priv->regmap, priv->reg, priv->idx,

priv->idx);

}

static void ti_syscon_gate_clk_disable(struct clk_hw *hw)

{

struct ti_syscon_gate_clk_priv *priv = to_ti_syscon_gate_clk_priv(hw);

regmap_write_bits(priv->regmap, priv->reg, priv->idx, 0);

}

static int ti_syscon_gate_clk_is_enabled(struct clk_hw *hw)

{

unsigned int val;

struct ti_syscon_gate_clk_priv *priv = to_ti_syscon_gate_clk_priv(hw);

regmap_read(priv->regmap, priv->reg, &val);

return !!(val & priv->idx);

}

static const struct clk_ops ti_syscon_gate_clk_ops = {

.enable = ti_syscon_gate_clk_enable,

.disable = ti_syscon_gate_clk_disable,

.is_enabled = ti_syscon_gate_clk_is_enabled,

};

static struct clk_hw

*ti_syscon_gate_clk_register(struct device *dev, struct regmap *regmap,

const char *parent_name,

const struct ti_syscon_gate_clk_data *data)

{

struct ti_syscon_gate_clk_priv *priv;

struct clk_init_data init;

char *name = NULL;

int ret;

priv = devm_kzalloc(dev, sizeof(*priv), GFP_KERNEL);

if (!priv)

return ERR_PTR(-ENOMEM);

init.ops = &ti_syscon_gate_clk_ops;

if (parent_name) {

name = kasprintf(GFP_KERNEL, "%s:%s", data->name, parent_name);

init.name = name;

init.parent_names = &parent_name;

init.num_parents = 1;

init.flags = CLK_SET_RATE_PARENT;

} else {

init.name = data->name;

init.parent_names = NULL;

init.num_parents = 0;

init.flags = 0;

}

priv->regmap = regmap;

priv->reg = data->offset;

priv->idx = BIT(data->bit_idx);

priv->hw.init = &init;

ret = devm_clk_hw_register(dev, &priv->hw);

if (name)

kfree(init.name);

if (ret)

return ERR_PTR(ret);

return &priv->hw;

}

static int ti_syscon_gate_clk_probe(struct platform_device *pdev)

{

const struct ti_syscon_gate_clk_data *data, *p;

struct clk_hw_onecell_data *hw_data;

struct device *dev = &pdev->dev;

int num_clks, num_parents, i;

const char *parent_name;

struct regmap *regmap;

data = device_get_match_data(dev);

if (!data)

return -EINVAL;

regmap = device_node_to_regmap(dev->of_node);

if (IS_ERR(regmap))

return dev_err_probe(dev, PTR_ERR(regmap),

"failed to get regmap\n");

num_clks = 0;

for (p = data; p->name; p++)

num_clks++;

num_parents = of_clk_get_parent_count(dev->of_node);

if (of_device_is_compatible(dev->of_node, "ti,am62-audio-refclk") &&

num_parents == 0) {

return dev_err_probe(dev, -EINVAL,

"must specify a parent clock\n");

}

hw_data = devm_kzalloc(dev, struct_size(hw_data, hws, num_clks),

GFP_KERNEL);

if (!hw_data)

return -ENOMEM;

hw_data->num = num_clks;

parent_name = of_clk_get_parent_name(dev->of_node, 0);

for (i = 0; i < num_clks; i++) {

hw_data->hws[i] = ti_syscon_gate_clk_register(dev, regmap,

parent_name,

&data[i]);

if (IS_ERR(hw_data->hws[i]))

dev_warn(dev, "failed to register %s\n",

data[i].name);

}

if (num_clks == 1)

return devm_of_clk_add_hw_provider(dev, of_clk_hw_simple_get,

hw_data->hws[0]);

else

return devm_of_clk_add_hw_provider(dev, of_clk_hw_onecell_get,

hw_data);

}

#define TI_SYSCON_CLK_GATE(_name, _offset, _bit_idx) \

{ \

.name = _name, \

.offset = (_offset), \

.bit_idx = (_bit_idx), \

}

static const struct ti_syscon_gate_clk_data am654_clk_data[] = {

TI_SYSCON_CLK_GATE("ehrpwm_tbclk0", 0x0, 0),

TI_SYSCON_CLK_GATE("ehrpwm_tbclk1", 0x4, 0),

TI_SYSCON_CLK_GATE("ehrpwm_tbclk2", 0x8, 0),

TI_SYSCON_CLK_GATE("ehrpwm_tbclk3", 0xc, 0),

TI_SYSCON_CLK_GATE("ehrpwm_tbclk4", 0x10, 0),

TI_SYSCON_CLK_GATE("ehrpwm_tbclk5", 0x14, 0),

{ /* Sentinel */ },

};

static const struct ti_syscon_gate_clk_data am64_clk_data[] = {

TI_SYSCON_CLK_GATE("epwm_tbclk0", 0x0, 0),

TI_SYSCON_CLK_GATE("epwm_tbclk1", 0x0, 1),

TI_SYSCON_CLK_GATE("epwm_tbclk2", 0x0, 2),

TI_SYSCON_CLK_GATE("epwm_tbclk3", 0x0, 3),

TI_SYSCON_CLK_GATE("epwm_tbclk4", 0x0, 4),

TI_SYSCON_CLK_GATE("epwm_tbclk5", 0x0, 5),

TI_SYSCON_CLK_GATE("epwm_tbclk6", 0x0, 6),

TI_SYSCON_CLK_GATE("epwm_tbclk7", 0x0, 7),

TI_SYSCON_CLK_GATE("epwm_tbclk8", 0x0, 8),

{ /* Sentinel */ },

};

static const struct ti_syscon_gate_clk_data am62_clk_data[] = {

TI_SYSCON_CLK_GATE("epwm_tbclk0", 0x0, 0),

TI_SYSCON_CLK_GATE("epwm_tbclk1", 0x0, 1),

TI_SYSCON_CLK_GATE("epwm_tbclk2", 0x0, 2),

{ /* Sentinel */ },

};

static const struct ti_syscon_gate_clk_data am62_audio_clk_data[] = {

TI_SYSCON_CLK_GATE("audio_refclk", 0x0, 15),

{ /* Sentinel */ },

};

static const struct of_device_id ti_syscon_gate_clk_ids[] = {

{

.compatible = "ti,am654-ehrpwm-tbclk",

.data = &am654_clk_data,

},

{

.compatible = "ti,am64-epwm-tbclk",

.data = &am64_clk_data,

},

{

.compatible = "ti,am62-epwm-tbclk",

.data = &am62_clk_data,

},

{

.compatible = "ti,am62-audio-refclk",

.data = &am62_audio_clk_data,

},

{ }

};

MODULE_DEVICE_TABLE(of, ti_syscon_gate_clk_ids);

static struct platform_driver ti_syscon_gate_clk_driver = {

.probe = ti_syscon_gate_clk_probe,

.driver = {

.name = "ti-syscon-gate-clk",

.of_match_table = ti_syscon_gate_clk_ids,

},

};

module_platform_driver(ti_syscon_gate_clk_driver);

MODULE_AUTHOR("Vignesh Raghavendra <vigneshr@ti.com>");

MODULE_DESCRIPTION("Syscon backed gate-clock driver");

MODULE_LICENSE("GPL");

Modification 2: Add the audio_refclk node in k3-am62-main.dtsidiff --git a/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/arch/arm64/boot/dts/ti/k3-am62-main.dtsi b/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/arch/arm64/boot/dts/ti/k3-am62-main.dtsi

index 510775e..b6f1905 100755

--- a/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/arch/arm64/boot/dts/ti/k3-am62-main.dtsi

+++ b/ti-processor-sdk-linux-rt-am62xx-evm-08.06.00.42/board-support/linux-rt-5.10.168+gitAUTOINC+c1a1291911-gc1a1291911/arch/arm64/boot/dts/ti/k3-am62-main.dtsi

@@ -61,6 +61,24 @@

#clock-cells = <1>;

};

+ audio_refclk0: clock-controller@82e0 {

+ compatible = "ti,am62-audio-refclk";

+ reg = <0x82e0 0x4>;

+ clocks = <&k3_clks 157 0>;

+ assigned-clocks = <&k3_clks 157 0>;

+ assigned-clock-parents = <&k3_cilks 157 8>;

+ #clock-cells = <0>;

+ };

+

+ audio_refclk1: clock-controller@82e4 {

+ compatible = "ti,am62-audio-refclk";

+ reg = <0x82e4 0x4>;

+ clocks = <&k3_clks 157 10>;

+ assigned-clocks = <&k3_clks 157 10>;

+ assigned-clock-parents = <&k3_clks 157 18>;

+ #clock-cells = <0>;

+ };

+

dss_oldi_io_ctrl: dss-oldi-io-ctrl@8600 {

compatible = "syscon";

reg = <0x8600 0x200>;

Modification 3: Add a custom device tree file

// SPDX-License-Identifier: GPL-2.0

/**

* DT overlay for Audio in main domain on AM62x SK

*

* Copyright (C) 2022 Texas Instruments Incorporated - https://www.ti.com/

*/

#include <dt-bindings/pinctrl/k3.h>

&{/} {

codec_audio: sound {

compatible = "simple-audio-card";

simple-audio-card,name = "AM62x-SKEVM-MASTER";

simple-audio-card,widgets =

"Headphone", "Headphone Jack",

"Microphone", "Microphone Jack";

simple-audio-card,routing =

"Headphone Jack", "HPLOUT",

"Headphone Jack", "HPROUT",

"MIC3L", "Microphone Jack",

"MIC3R", "Microphone Jack",

"Microphone Jack", "Mic Bias";

simple-audio-card,format = "i2s";

simple-audio-card,bitclock-master = <&sound_master>;

simple-audio-card,frame-master = <&sound_master>;

simple-audio-card,mclk-fs = <512>;

sound_master: simple-audio-card,cpu {

sound-dai = <&mcasp1>;

system-clock-direction-out;

};

simple-audio-card,codec {

sound-dai = <&tlv320aic3101>;

clocks = <&audio_refclk1>;

};

};

};

&main_pmx0 {

main_mcasp1_rst_pins_default: main-mcasp1-rst-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x007c, PIN_OUTPUT, 7) /* (P25) GPMC0_CLK.GPIO0_31 */

>;

};

main_mcasp1_pins_default: main-mcasp1-pins-default {

pinctrl-single,pins = <

AM62X_IOPAD(0x01a8, PIN_OUTPUT, 2) /* (D20) MCASP0_AFSX.AUDIO_EXT_REFCLK1 */

AM62X_IOPAD(0x0024, PIN_OUTPUT, 2) /* (H25) OSPI0_D6.MCASP1_ACLKX */

AM62X_IOPAD(0x0028, PIN_OUTPUT, 2) /* (J22) OSPI0_D7.MCASP1_AFSX */

AM62X_IOPAD(0x0020, PIN_INPUT, 2) /* (J25) OSPI0_D5.MCASP1_AXR0 */

AM62X_IOPAD(0x001c, PIN_OUTPUT, 2) /* (J23) OSPI0_D4.MCASP1_AXR1 */

>;

};

};

&mcasp0 {

status = "disabled";

};

&mcasp1 {

status = "okay";

#sound-dai-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&main_mcasp1_pins_default &main_mcasp1_rst_pins_default>;

op-mode = <0>; /* MCASP_IIS_MODE */

tdm-slots = <2>;

serial-dir = < /* 0: INACTIVE, 1: TX, 2: RX */

2 1 0 0

0 0 0 0

0 0 0 0

0 0 0 0

>;

tx-num-evt = <32>;

rx-num-evt = <32>;

};

&mcasp2 {

status = "disabled";

};

&main_i2c2 {

tlv320aic3101: audio-codec@18 {

#sound-dai-cells = <0>;

compatible = "ti,tlv320aic3x";

reg = <0x18>;

ai3x-micbias-vg = <1>; /* 2.0V */

reset-gpios = <&main_gpio0 31 GPIO_ACTIVE_LOW>;

status = "okay";

/* Regulators */

AVDD-supply = <&vcc_3v3_sys>;

IOVDD-supply = <&vcc_3v3_sys>;

DRVDD-supply = <&vcc_3v3_sys>;

DVDD-supply = <&vcc_1v8>;

};

};

// Set AUDIO_EXT_REFCLK1 to 25MHz

&audio_refclk1 {

assigned-clock-rates = <25000000>;

};

I used the following command for recording test:

root@am62xx:~# time arecord -f S16_LE -c 2 -r 22050 -d 10 -t wav record.wav

Recording WAVE 'record.wav' : Signed 16 bit Little Endian, Rate 22050 Hz, Stereo

real 0m 4.84s

user 0m 0.41s

sys 0m 0.03s

From the above test log, it can be noticed that the command used was to record 10 seconds of audio data, but it actually only recorded for 4.84 seconds before ending.

There is obviously a problem here, so I used the following command to check the corresponding clock:

root@am62xx:~# k3conf dump clock 157

|--------------------------------------------------------------------------------|

| VERSION INFO |

|--------------------------------------------------------------------------------|

| K3CONF | (version v0.1-88-g982f5c2 built Mon Jun 26 06:16:37 UTC 2023) |

| SoC | AM62X SR1.0 |

| SYSFW | ABI: 3.1 (firmware version 0x0008 '8.6.4--v08.06.04 (Chill Capybar)') |

|--------------------------------------------------------------------------------|

autoadjust_table_generic_fprint(): WARNING: "DEV_BOARD0_OBSCLK0_IN_PARENT_SAM62_A53_512KB_WRAP_MAIN_0_ARM_COREPACK_0_A53_DIVH_CLK4_OBSCLK_OUT_CLKCLK_STATE_READY" size (115) > TABLE_MAX_ELT_LEN (100)!

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device ID | Clock ID | Clock Name | Status | Clock Frequency |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 157 | 0 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN | CLK_STATE_READY | 45454545 |

| 157 | 1 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_MCASP_MAIN_0_MCASP_AHCLKR_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 2 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_MCASP_MAIN_1_MCASP_AHCLKR_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 3 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_MCASP_MAIN_2_MCASP_AHCLKR_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 4 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_MCASP_MAIN_0_MCASP_AHCLKX_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 5 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_MCASP_MAIN_1_MCASP_AHCLKX_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 6 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_MCASP_MAIN_2_MCASP_AHCLKX_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 7 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_POSTDIV1_16FFT_MAIN_1_HSDIVOUT6_CLK | CLK_STATE_READY | 96000000 |

| 157 | 8 | DEV_BOARD0_AUDIO_EXT_REFCLK0_IN_PARENT_POSTDIV4_16FF_MAIN_2_HSDIVOUT8_CLK | CLK_STATE_READY | 45454545 |

| 157 | 9 | DEV_BOARD0_AUDIO_EXT_REFCLK0_OUT | CLK_STATE_READY | 0 |

| 157 | 10 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN | CLK_STATE_READY | 45454545 |

| 157 | 11 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_MCASP_MAIN_0_MCASP_AHCLKR_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 12 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_MCASP_MAIN_1_MCASP_AHCLKR_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 13 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_MCASP_MAIN_2_MCASP_AHCLKR_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 14 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_MCASP_MAIN_0_MCASP_AHCLKX_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 15 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_MCASP_MAIN_1_MCASP_AHCLKX_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 16 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_MCASP_MAIN_2_MCASP_AHCLKX_POUT | CLK_STATE_NOT_READY | 0 |

| 157 | 17 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_POSTDIV1_16FFT_MAIN_1_HSDIVOUT6_CLK | CLK_STATE_READY | 96000000 |

| 157 | 18 | DEV_BOARD0_AUDIO_EXT_REFCLK1_IN_PARENT_POSTDIV4_16FF_MAIN_2_HSDIVOUT8_CLK | CLK_STATE_READY | 45454545 |

| 157 | 19 | DEV_BOARD0_AUDIO_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 157 | 20 | DEV_BOARD0_CLKOUT0_IN | CLK_STATE_READY | 50000000 |

| 157 | 21 | DEV_BOARD0_CLKOUT0_IN_PARENT_HSDIV4_16FFT_MAIN_2_HSDIVOUT1_CLK5 | CLK_STATE_READY | 50000000 |

| 157 | 22 | DEV_BOARD0_CLKOUT0_IN_PARENT_HSDIV4_16FFT_MAIN_2_HSDIVOUT1_CLK10 | CLK_STATE_READY | 25000000 |

| 157 | 23 | DEV_BOARD0_CP_GEMAC_CPTS0_RFT_CLK_OUT | CLK_STATE_READY | 0 |

| 157 | 24 | DEV_BOARD0_DDR0_CK0_IN | CLK_STATE_READY | 250000000 |

| 157 | 25 | DEV_BOARD0_DDR0_CK0_N_IN | CLK_STATE_READY | 0 |

| 157 | 27 | DEV_BOARD0_DDR0_CK0_OUT | CLK_STATE_READY | 0 |

| 157 | 33 | DEV_BOARD0_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 157 | 34 | DEV_BOARD0_GPMC0_CLKLB_IN | CLK_STATE_READY | 0 |

| 157 | 35 | DEV_BOARD0_GPMC0_CLKLB_OUT | CLK_STATE_READY | 0 |

| 157 | 36 | DEV_BOARD0_GPMC0_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 37 | DEV_BOARD0_GPMC0_FCLK_MUX_IN | CLK_STATE_READY | 133333333 |

| 157 | 38 | DEV_BOARD0_GPMC0_FCLK_MUX_IN_PARENT_HSDIV4_16FFT_MAIN_0_HSDIVOUT3_CLK | CLK_STATE_READY | 133333333 |

| 157 | 39 | DEV_BOARD0_GPMC0_FCLK_MUX_IN_PARENT_POSTDIV4_16FF_MAIN_2_HSDIVOUT7_CLK | CLK_STATE_READY | 100000000 |

| 157 | 40 | DEV_BOARD0_I2C0_SCL_IN | CLK_STATE_READY | 0 |

| 157 | 41 | DEV_BOARD0_I2C0_SCL_OUT | CLK_STATE_READY | 0 |

| 157 | 42 | DEV_BOARD0_I2C1_SCL_IN | CLK_STATE_READY | 0 |

| 157 | 43 | DEV_BOARD0_I2C1_SCL_OUT | CLK_STATE_READY | 0 |

| 157 | 44 | DEV_BOARD0_I2C2_SCL_IN | CLK_STATE_READY | 0 |

| 157 | 45 | DEV_BOARD0_I2C2_SCL_OUT | CLK_STATE_READY | 0 |

| 157 | 46 | DEV_BOARD0_I2C3_SCL_IN | CLK_STATE_READY | 0 |

| 157 | 47 | DEV_BOARD0_I2C3_SCL_OUT | CLK_STATE_READY | 0 |

| 157 | 49 | DEV_BOARD0_MCASP0_ACLKR_IN | CLK_STATE_READY | 0 |

| 157 | 50 | DEV_BOARD0_MCASP0_ACLKR_OUT | CLK_STATE_READY | 0 |

| 157 | 51 | DEV_BOARD0_MCASP0_ACLKX_IN | CLK_STATE_READY | 0 |

| 157 | 52 | DEV_BOARD0_MCASP0_ACLKX_OUT | CLK_STATE_READY | 0 |

| 157 | 53 | DEV_BOARD0_MCASP0_AFSR_IN | CLK_STATE_READY | 0 |

| 157 | 54 | DEV_BOARD0_MCASP0_AFSX_IN | CLK_STATE_READY | 0 |

| 157 | 55 | DEV_BOARD0_MCASP1_ACLKR_IN | CLK_STATE_READY | 0 |

| 157 | 56 | DEV_BOARD0_MCASP1_ACLKR_OUT | CLK_STATE_READY | 0 |

| 157 | 57 | DEV_BOARD0_MCASP1_ACLKX_IN | CLK_STATE_READY | 0 |

| 157 | 58 | DEV_BOARD0_MCASP1_ACLKX_OUT | CLK_STATE_READY | 0 |

| 157 | 59 | DEV_BOARD0_MCASP1_AFSR_IN | CLK_STATE_READY | 0 |

| 157 | 60 | DEV_BOARD0_MCASP1_AFSX_IN | CLK_STATE_READY | 0 |

| 157 | 61 | DEV_BOARD0_MCASP2_ACLKR_IN | CLK_STATE_READY | 0 |

| 157 | 62 | DEV_BOARD0_MCASP2_ACLKR_OUT | CLK_STATE_READY | 0 |

| 157 | 63 | DEV_BOARD0_MCASP2_ACLKX_IN | CLK_STATE_READY | 0 |

| 157 | 64 | DEV_BOARD0_MCASP2_ACLKX_OUT | CLK_STATE_READY | 0 |

| 157 | 65 | DEV_BOARD0_MCASP2_AFSR_IN | CLK_STATE_READY | 0 |

| 157 | 66 | DEV_BOARD0_MCASP2_AFSX_IN | CLK_STATE_READY | 0 |

| 157 | 67 | DEV_BOARD0_MCU_EXT_REFCLK0_OUT | CLK_STATE_READY | 0 |

| 157 | 68 | DEV_BOARD0_MCU_I2C0_SCL_IN | CLK_STATE_READY | 0 |

| 157 | 69 | DEV_BOARD0_MCU_I2C0_SCL_OUT | CLK_STATE_READY | 0 |

| 157 | 70 | DEV_BOARD0_MCU_OBSCLK0_IN | CLK_STATE_READY | 12500000 |

| 157 | 71 | DEV_BOARD0_MCU_OBSCLK0_IN_PARENT_MCU_OBSCLK_DIV_OUT0 | CLK_STATE_READY | 12500000 |

| 157 | 72 | DEV_BOARD0_MCU_OBSCLK0_IN_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 25000000 |

| 157 | 73 | DEV_BOARD0_MCU_SPI0_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 75 | DEV_BOARD0_MCU_SPI1_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 77 | DEV_BOARD0_MCU_SYSCLKOUT0_IN | CLK_STATE_READY | 100000000 |

| 157 | 78 | DEV_BOARD0_MCU_TIMER_IO0_IN | CLK_STATE_READY | 0 |

| 157 | 79 | DEV_BOARD0_MCU_TIMER_IO1_IN | CLK_STATE_READY | 0 |

| 157 | 80 | DEV_BOARD0_MCU_TIMER_IO2_IN | CLK_STATE_READY | 0 |

| 157 | 81 | DEV_BOARD0_MCU_TIMER_IO3_IN | CLK_STATE_READY | 0 |

| 157 | 82 | DEV_BOARD0_MDIO0_MDC_IN | CLK_STATE_READY | 0 |

| 157 | 83 | DEV_BOARD0_MMC0_CLKLB_IN | CLK_STATE_READY | 0 |

| 157 | 84 | DEV_BOARD0_MMC0_CLKLB_OUT | CLK_STATE_READY | 0 |

| 157 | 86 | DEV_BOARD0_MMC0_CLK_OUT | CLK_STATE_READY | 0 |

| 157 | 87 | DEV_BOARD0_MMC1_CLKLB_IN | CLK_STATE_READY | 0 |

| 157 | 88 | DEV_BOARD0_MMC1_CLKLB_OUT | CLK_STATE_READY | 0 |

| 157 | 89 | DEV_BOARD0_MMC1_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 90 | DEV_BOARD0_MMC1_CLK_OUT | CLK_STATE_READY | 0 |

| 157 | 91 | DEV_BOARD0_MMC2_CLKLB_IN | CLK_STATE_READY | 0 |

| 157 | 92 | DEV_BOARD0_MMC2_CLKLB_OUT | CLK_STATE_READY | 0 |

| 157 | 93 | DEV_BOARD0_MMC2_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 94 | DEV_BOARD0_MMC2_CLK_OUT | CLK_STATE_READY | 0 |

| 157 | 95 | DEV_BOARD0_OBSCLK0_IN | CLK_STATE_READY | 500000000 |

| 157 | 96 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV4_16FFT_MAIN_0_HSDIVOUT0_CLK | CLK_STATE_READY | 500000000 |

| 157 | 97 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV4_16FFT_MAIN_1_HSDIVOUT0_CLK | CLK_STATE_READY | 192000000 |

| 157 | 98 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV4_16FFT_MAIN_2_HSDIVOUT0_CLK | CLK_STATE_READY | 333333333 |

| 157 | 99 | DEV_BOARD0_OBSCLK0_IN_PARENT_SAM62_A53_512KB_WRAP_MAIN_0_ARM_COREPACK_0_A53_DIVH_CLK4_OBSCLK_OUT_CLK | CLK_STATE_READY | 0 |

| 157 | 100 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV0_16FFT_MAIN_12_HSDIVOUT0_CLK | CLK_STATE_READY | 400000000 |

| 157 | 101 | DEV_BOARD0_OBSCLK0_IN_PARENT_GLUELOGIC_RCOSC_CLKOUT | CLK_STATE_READY | 12500000 |

| 157 | 102 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV0_16FFT_MCU_32KHZ_GEN_0_HSDIVOUT0_CLK8 | CLK_STATE_READY | 30637 |

| 157 | 103 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV4_16FFT_MAIN_0_HSDIVOUT0_CLK_DUP0 | CLK_STATE_READY | 500000000 |

| 157 | 104 | DEV_BOARD0_OBSCLK0_IN_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 25000000 |

| 157 | 105 | DEV_BOARD0_OBSCLK0_IN_PARENT_MAIN_OBSCLK0_MUX_SEL_DIV_CLKOUT | CLK_STATE_READY | 32552 |

| 157 | 106 | DEV_BOARD0_OBSCLK0_IN_PARENT_CPSW_3GUSS_MAIN_0_CPTS_GENF0 | CLK_STATE_READY | 0 |

| 157 | 107 | DEV_BOARD0_OBSCLK0_IN_PARENT_CPSW_3GUSS_MAIN_0_CPTS_GENF1 | CLK_STATE_READY | 0 |

| 157 | 108 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV4_16FFT_MCU_0_HSDIVOUT0_CLK | CLK_STATE_READY | 400000000 |

| 157 | 109 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV1_16FFT_MAIN_15_HSDIVOUT0_CLK | CLK_STATE_READY | 400000000 |

| 157 | 110 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV0_16FFT_MAIN_16_HSDIVOUT0_CLK | CLK_STATE_READY | 297500000 |

| 157 | 111 | DEV_BOARD0_OBSCLK0_IN_PARENT_HSDIV0_16FFT_MAIN_17_HSDIVOUT0_CLK | CLK_STATE_READY | 170000000 |

| 157 | 112 | DEV_BOARD0_OBSCLK0_IN_PARENT_SAM62_PLL_CTRL_WRAP_MAIN_0_CHIP_DIV1_CLK_CLK | CLK_STATE_READY | 500000000 |

| 157 | 113 | DEV_BOARD0_OBSCLK0_IN_PARENT_CLK_32K_RC_SEL_OUT0 | CLK_STATE_READY | 32768 |

| 157 | 128 | DEV_BOARD0_OSPI0_DQS_OUT | CLK_STATE_READY | 0 |

| 157 | 129 | DEV_BOARD0_OSPI0_LBCLKO_IN | CLK_STATE_READY | 0 |

| 157 | 130 | DEV_BOARD0_OSPI0_LBCLKO_OUT | CLK_STATE_READY | 0 |

| 157 | 131 | DEV_BOARD0_RGMII1_RXC_OUT | CLK_STATE_READY | 0 |

| 157 | 132 | DEV_BOARD0_RGMII1_TXC_IN | CLK_STATE_READY | 0 |

| 157 | 133 | DEV_BOARD0_RGMII1_TXC_OUT | CLK_STATE_READY | 0 |

| 157 | 134 | DEV_BOARD0_RGMII2_RXC_OUT | CLK_STATE_READY | 0 |

| 157 | 135 | DEV_BOARD0_RGMII2_TXC_IN | CLK_STATE_READY | 0 |

| 157 | 136 | DEV_BOARD0_RGMII2_TXC_OUT | CLK_STATE_READY | 0 |

| 157 | 137 | DEV_BOARD0_RMII1_REF_CLK_OUT | CLK_STATE_READY | 0 |

| 157 | 138 | DEV_BOARD0_RMII2_REF_CLK_OUT | CLK_STATE_READY | 0 |

| 157 | 139 | DEV_BOARD0_SPI0_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 141 | DEV_BOARD0_SPI1_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 143 | DEV_BOARD0_SPI2_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 145 | DEV_BOARD0_SYSCLKOUT0_IN | CLK_STATE_READY | 125000000 |

| 157 | 146 | DEV_BOARD0_TCK_OUT | CLK_STATE_READY | 0 |

| 157 | 147 | DEV_BOARD0_TIMER_IO0_IN | CLK_STATE_READY | 0 |

| 157 | 148 | DEV_BOARD0_TIMER_IO1_IN | CLK_STATE_READY | 0 |

| 157 | 149 | DEV_BOARD0_TIMER_IO2_IN | CLK_STATE_READY | 0 |

| 157 | 150 | DEV_BOARD0_TIMER_IO3_IN | CLK_STATE_READY | 0 |

| 157 | 151 | DEV_BOARD0_TIMER_IO4_IN | CLK_STATE_READY | 0 |

| 157 | 152 | DEV_BOARD0_TIMER_IO5_IN | CLK_STATE_READY | 0 |

| 157 | 153 | DEV_BOARD0_TIMER_IO6_IN | CLK_STATE_READY | 0 |

| 157 | 154 | DEV_BOARD0_TIMER_IO7_IN | CLK_STATE_READY | 0 |

| 157 | 155 | DEV_BOARD0_TRC_CLK_IN | CLK_STATE_READY | 0 |

| 157 | 156 | DEV_BOARD0_VOUT0_EXTPCLKIN_OUT | CLK_STATE_READY | 0 |

| 157 | 157 | DEV_BOARD0_VOUT0_PCLK_IN | CLK_STATE_READY | 0 |

| 157 | 158 | DEV_BOARD0_WKUP_CLKOUT0_IN | CLK_STATE_READY | 32768 |

| 157 | 159 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 25000000 |

| 157 | 160 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_GLUELOGIC_LFOSC0_CLKOUT | CLK_STATE_READY | 32768 |

| 157 | 161 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_HSDIV4_16FFT_MAIN_0_HSDIVOUT2_CLK | CLK_STATE_READY | 200000000 |

| 157 | 162 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_HSDIV4_16FFT_MAIN_1_HSDIVOUT2_CLK | CLK_STATE_READY | 192000000 |

| 157 | 163 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_POSTDIV4_16FF_MAIN_2_HSDIVOUT9_CLK | CLK_STATE_READY | 50000000 |

| 157 | 164 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_CLK_32K_RC_SEL_OUT0 | CLK_STATE_READY | 32768 |

| 157 | 165 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_GLUELOGIC_RCOSC_CLKOUT | CLK_STATE_READY | 12500000 |

| 157 | 166 | DEV_BOARD0_WKUP_CLKOUT0_IN_PARENT_GLUELOGIC_HFOSC0_CLKOUT_DUP0 | CLK_STATE_READY | 25000000 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

root@am62xx:~# k3conf dump clock 191

|--------------------------------------------------------------------------------|

| VERSION INFO |

|--------------------------------------------------------------------------------|

| K3CONF | (version v0.1-88-g982f5c2 built Mon Jun 26 06:16:37 UTC 2023) |

| SoC | AM62X SR1.0 |

| SYSFW | ABI: 3.1 (firmware version 0x0008 '8.6.4--v08.06.04 (Chill Capybar)') |

|--------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------|

| Device ID | Clock ID | Clock Name | Status | Clock Frequency |

|-----------------------------------------------------------------------------------------------------------------------------|

| 191 | 0 | DEV_MCASP1_AUX_CLK | CLK_STATE_READY | 96000000 |

| 191 | 1 | DEV_MCASP1_AUX_CLK_PARENT_POSTDIV4_16FF_MAIN_2_HSDIVOUT8_CLK | CLK_STATE_READY | 45454545 |

| 191 | 2 | DEV_MCASP1_AUX_CLK_PARENT_POSTDIV1_16FFT_MAIN_1_HSDIVOUT6_CLK | CLK_STATE_READY | 96000000 |

| 191 | 3 | DEV_MCASP1_MCASP_ACLKR_PIN | CLK_STATE_READY | 0 |

| 191 | 4 | DEV_MCASP1_MCASP_ACLKR_POUT | CLK_STATE_READY | 0 |

| 191 | 5 | DEV_MCASP1_MCASP_ACLKX_PIN | CLK_STATE_READY | 0 |

| 191 | 6 | DEV_MCASP1_MCASP_ACLKX_POUT | CLK_STATE_READY | 0 |

| 191 | 7 | DEV_MCASP1_MCASP_AFSR_POUT | CLK_STATE_READY | 0 |

| 191 | 8 | DEV_MCASP1_MCASP_AFSX_POUT | CLK_STATE_READY | 0 |

| 191 | 9 | DEV_MCASP1_MCASP_AHCLKR_PIN | CLK_STATE_READY | 0 |

| 191 | 10 | DEV_MCASP1_MCASP_AHCLKR_PIN_PARENT_BOARD_0_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 191 | 11 | DEV_MCASP1_MCASP_AHCLKR_PIN_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 25000000 |

| 191 | 12 | DEV_MCASP1_MCASP_AHCLKR_PIN_PARENT_BOARD_0_AUDIO_EXT_REFCLK0_OUT | CLK_STATE_READY | 0 |

| 191 | 13 | DEV_MCASP1_MCASP_AHCLKR_PIN_PARENT_BOARD_0_AUDIO_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 191 | 14 | DEV_MCASP1_MCASP_AHCLKR_POUT | CLK_STATE_READY | 0 |

| 191 | 15 | DEV_MCASP1_MCASP_AHCLKX_PIN | CLK_STATE_READY | 0 |

| 191 | 16 | DEV_MCASP1_MCASP_AHCLKX_PIN_PARENT_BOARD_0_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 191 | 17 | DEV_MCASP1_MCASP_AHCLKX_PIN_PARENT_GLUELOGIC_HFOSC0_CLKOUT | CLK_STATE_READY | 25000000 |

| 191 | 18 | DEV_MCASP1_MCASP_AHCLKX_PIN_PARENT_BOARD_0_AUDIO_EXT_REFCLK0_OUT | CLK_STATE_READY | 0 |

| 191 | 19 | DEV_MCASP1_MCASP_AHCLKX_PIN_PARENT_BOARD_0_AUDIO_EXT_REFCLK1_OUT | CLK_STATE_READY | 0 |

| 191 | 20 | DEV_MCASP1_MCASP_AHCLKX_POUT | CLK_STATE_READY | 0 |

| 191 | 21 | DEV_MCASP1_VBUSP_CLK | CLK_STATE_READY | 250000000 |

|-----------------------------------------------------------------------------------------------------------------------------|

Simultaneously check the relevant registers, and the results are as follows:

root@am62xx:~# devmem2 0x02B100AC

/dev/mem opened.

Memory mapped at address 0xffffa97b7000.

Bus error (core dumped)

root@am62xx:~# devmem2 0x02B100A8

/dev/mem opened.

Memory mapped at address 0xffffa8352000.

Bus error (core dumped)

root@am62xx:~# devmem2 0x001082E4

/dev/mem opened.

Memory mapped at address 0xffffafa5e000.

Read at address 0x001082E4 (0xffffafa5e2e4): 0x00000007

root@am62xx:~# devmem2 0x02B100B4

/dev/mem opened.

Memory mapped at address 0xffff9cc70000.

Bus error (core dumped)

root@am62xx:~# devmem2 0x02B100B0

/dev/mem opened.

Memory mapped at address 0xffff91f71000.

Bus error (core dumped)

root@am62xx:~# devmem2 0x00108334

/dev/mem opened.

Memory mapped at address 0xffffa4ca9000.

Read at address 0x00108334 (0xffffa4ca9334): 0x00000001

root@am62xx:~# devmem2 0x00681098

/dev/mem opened.

Memory mapped at address 0xffffbb0f0000.

Read at address 0x00681098 (0xffffbb0f0098): 0x00008009

root@am62xx:~# devmem2 0x006820A0

/dev/mem opened.

Memory mapped at address 0xffff94dda000.

Read at address 0x006820A0 (0xffff94dda0a0): 0x00008015

As shown in the above result, there is another issue here:

When I use the devmem2 command to read registers at 0x02B100AC, 0x02B100A8, 0x02B100B4, and 0x02B100B0, it returns an error and cannot read the values of the registers.

Finally, I also captured the relevant waveforms using an oscilloscope, as shown below:

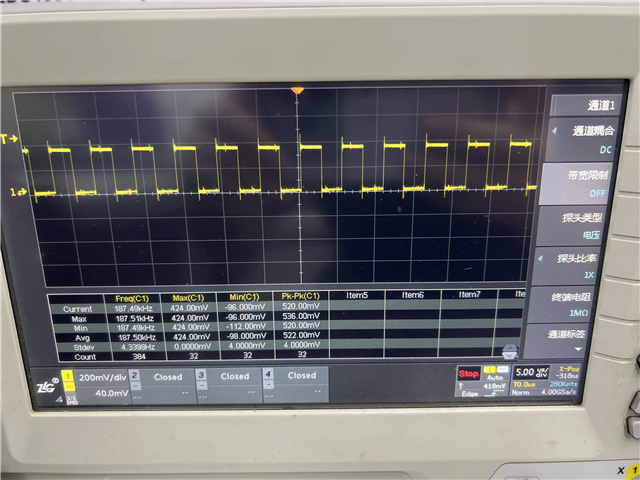

The waveform of the frame clock during audio recording:

From the waveform of the frame clock above, it can be seen that the frame clock generated by mcasp is incorrect. The frame clock generated by mcasp is 187.49Khz, while the correct clock frequency should be 22.05Khz.

I have reviewed the content of section 12.1.1.3.2.3 Frame-Sync Generator in the TRM (Technical Reference Manual),as shown below,but I'm still unclear about how the frame sync clock is specifically configured.

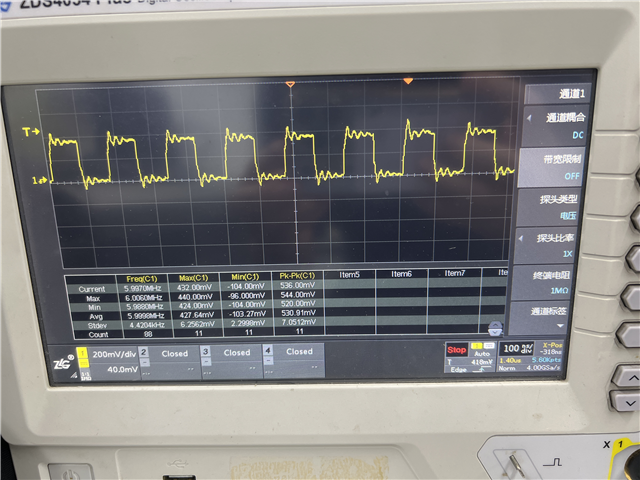

The waveform of the bit clock is shown below:

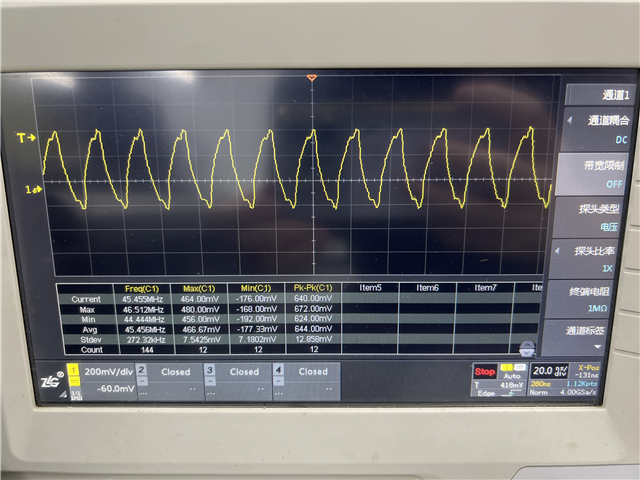

The waveform of the master clock is shown below:

Taking into account the above information, how should I modify the code and device tree to ensure that the mcasp outputs the correct frame clock, bit clock, and master clock, and to enable proper recording and playback?

Looking forward to your reply.

Regards,

Li