Hi

There's a question that customer wants to clarify about SERDES0_REFCLK.

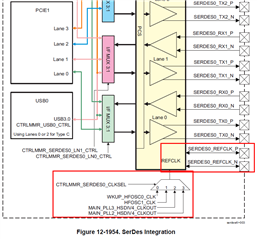

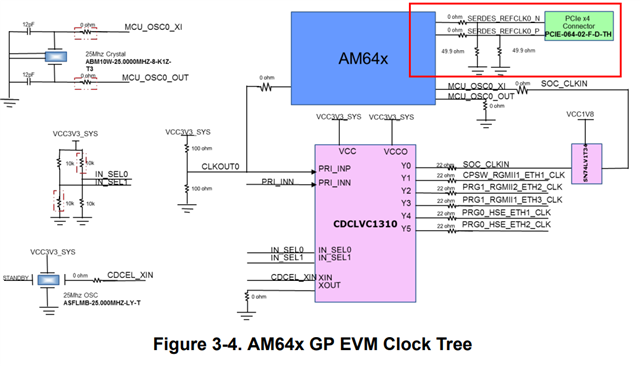

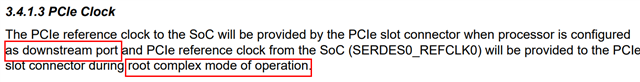

It seems the SERDES0_REFCLK ports can be bi-directional clock I/O pins which can be used for SGMII, PCIe and USB3.0.

From my initial review, I am able to find the CLK SEL register for SERDES0_REFCLK as below.

I supposed the refclk port can be configured as output with the selected internally routed clock source.

However I can not figure out the maximum output clock speed at SERDES0_REFCLK port if external clock generator is not mandatory.

Could you please clarify whether the SERDES0_REFCLK (output) port is able to connected to PCIe' REFCLK without a Clock Generator device such like PI6CFGL201BZDIE.?

If the use case above mentioned is allowed, please also clarify whether the serdes0_refclk can output up to 2Ghz

Customer supposed the clock speed can be sufficient with 2GHz for PCIe.

Thanks.