Other Parts Discussed in Thread: SYSCONFIG

Our custom design connects the MCU_RGMII1 interfaces of two TDA4 SOMs directly together using a buffer chip and board-to-board connectors. The signals are crossed-over (SOM1 TX <-> SOM2 RX), and I've configured Linux for fixed-link mode:

&cpsw_port1 {

phy-mode = "rgmii";

fixed-link {

speed = <100>;

full-duplex;

};

};

And confirmed the correct pinmux:

mcu_cpsw_pins_default: mcu_cpsw_pins_default {

pinctrl-single,pins = <

J721E_WKUP_IOPAD(0x0058, PIN_OUTPUT | DRV_STR_1, 0) /* MCU_RGMII1_TX_CTL */

J721E_WKUP_IOPAD(0x005c, PIN_INPUT, 0) /* MCU_RGMII1_RX_CTL */

J721E_WKUP_IOPAD(0x0060, PIN_OUTPUT | DRV_STR_1, 0) /* MCU_RGMII1_TD3 */

J721E_WKUP_IOPAD(0x0064, PIN_OUTPUT | DRV_STR_1, 0) /* MCU_RGMII1_TD2 */

J721E_WKUP_IOPAD(0x0068, PIN_OUTPUT | DRV_STR_1, 0) /* MCU_RGMII1_TD1 */

J721E_WKUP_IOPAD(0x006c, PIN_OUTPUT | DRV_STR_1, 0) /* MCU_RGMII1_TD0 */

J721E_WKUP_IOPAD(0x0078, PIN_INPUT, 0) /* MCU_RGMII1_RD3 */

J721E_WKUP_IOPAD(0x007c, PIN_INPUT, 0) /* MCU_RGMII1_RD2 */

J721E_WKUP_IOPAD(0x0080, PIN_INPUT, 0) /* MCU_RGMII1_RD1 */

J721E_WKUP_IOPAD(0x0084, PIN_INPUT, 0) /* MCU_RGMII1_RD0 */

J721E_WKUP_IOPAD(0x0070, PIN_INPUT | DRV_STR_1, 0) /* MCU_RGMII1_TXC */

J721E_WKUP_IOPAD(0x0074, PIN_INPUT, 0) /* MCU_RGMII1_RXC */

>;

};

Output from ethtool shows that the interface is up and attempting to transmit, but is not receiving (or even dropping) packets from the remote side: (same result on from both SOMs)

NIC statistics:

p0_rx_good_frames: 47

p0_rx_broadcast_frames: 23

p0_rx_multicast_frames: 24

p0_rx_crc_errors: 0

p0_rx_oversized_frames: 0

p0_rx_undersized_frames: 0

p0_ale_drop: 0

p0_ale_overrun_drop: 0

p0_rx_octets: 10870

p0_tx_good_frames: 0

p0_tx_broadcast_frames: 0

p0_tx_multicast_frames: 0

p0_tx_octets: 0

p0_tx_64B_frames: 2

p0_tx_65_to_127B_frames: 14

p0_tx_128_to_255B_frames: 8

p0_tx_256_to_511B_frames: 23

p0_tx_512_to_1023B_frames: 0

p0_tx_1024B_frames: 0

p0_net_octets: 10870

p0_rx_bottom_fifo_drop: 0

p0_rx_port_mask_drop: 0

p0_rx_top_fifo_drop: 0

p0_ale_rate_limit_drop: 0

p0_ale_vid_ingress_drop: 0

p0_ale_da_eq_sa_drop: 0

p0_ale_block_drop: 0

p0_ale_secure_drop: 0

p0_ale_auth_drop: 0

p0_ale_unknown_ucast: 0

p0_ale_unknown_ucast_bytes: 0

p0_ale_unknown_mcast: 0

p0_ale_unknown_mcast_bytes: 0

p0_ale_unknown_bcast: 0

p0_ale_unknown_bcast_bytes: 0

p0_ale_pol_match: 0

p0_ale_pol_match_red: 0

p0_ale_pol_match_yellow: 0

p0_ale_mcast_sa_drop: 0

p0_ale_dual_vlan_drop: 0

p0_ale_len_err_drop: 0

p0_ale_ip_next_hdr_drop: 0

p0_ale_ipv4_frag_drop: 0

p0_tx_mem_protect_err: 0

p0_tx_pri0: 0

p0_tx_pri1: 0

p0_tx_pri2: 0

p0_tx_pri3: 0

p0_tx_pri4: 0

p0_tx_pri5: 0

p0_tx_pri6: 0

p0_tx_pri7: 0

p0_tx_pri0_bcnt: 0

p0_tx_pri1_bcnt: 0

p0_tx_pri2_bcnt: 0

p0_tx_pri3_bcnt: 0

p0_tx_pri4_bcnt: 0

p0_tx_pri5_bcnt: 0

p0_tx_pri6_bcnt: 0

p0_tx_pri7_bcnt: 0

p0_tx_pri0_drop: 0

p0_tx_pri1_drop: 0

p0_tx_pri2_drop: 0

p0_tx_pri3_drop: 0

p0_tx_pri4_drop: 0

p0_tx_pri5_drop: 0

p0_tx_pri6_drop: 0

p0_tx_pri7_drop: 0

p0_tx_pri0_drop_bcnt: 0

p0_tx_pri1_drop_bcnt: 0

p0_tx_pri2_drop_bcnt: 0

p0_tx_pri3_drop_bcnt: 0

p0_tx_pri4_drop_bcnt: 0

p0_tx_pri5_drop_bcnt: 0

p0_tx_pri6_drop_bcnt: 0

p0_tx_pri7_drop_bcnt: 0

rx_good_frames: 0

rx_broadcast_frames: 0

rx_multicast_frames: 0

rx_pause_frames: 0

rx_crc_errors: 0

rx_align_code_errors: 0

rx_oversized_frames: 0

rx_jabber_frames: 0

rx_undersized_frames: 0

rx_fragments: 1

ale_drop: 0

ale_overrun_drop: 0

rx_octets: 0

tx_good_frames: 47

tx_broadcast_frames: 23

tx_multicast_frames: 24

tx_pause_frames: 0

tx_deferred_frames: 0

tx_collision_frames: 0

tx_single_coll_frames: 0

tx_mult_coll_frames: 0

tx_excessive_collisions: 0

tx_late_collisions: 0

rx_ipg_error: 0

tx_carrier_sense_errors: 0

tx_octets: 10870

tx_64B_frames: 2

tx_65_to_127B_frames: 14

tx_128_to_255B_frames: 8

tx_256_to_511B_frames: 23

tx_512_to_1023B_frames: 0

tx_1024B_frames: 0

net_octets: 10873

rx_bottom_fifo_drop: 0

rx_port_mask_drop: 0

rx_top_fifo_drop: 0

ale_rate_limit_drop: 0

ale_vid_ingress_drop: 0

ale_da_eq_sa_drop: 0

ale_block_drop: 0

ale_secure_drop: 0

ale_auth_drop: 0

ale_unknown_ucast: 0

ale_unknown_ucast_bytes: 0

ale_unknown_mcast: 0

ale_unknown_mcast_bytes: 0

ale_unknown_bcast: 0

ale_unknown_bcast_bytes: 0

ale_pol_match: 0

ale_pol_match_red: 0

ale_pol_match_yellow: 0

ale_mcast_sa_drop: 0

ale_dual_vlan_drop: 0

ale_len_err_drop: 0

ale_ip_next_hdr_drop: 0

ale_ipv4_frag_drop: 0

iet_rx_assembly_err: 0

iet_rx_assembly_ok: 0

iet_rx_smd_err: 653

iet_rx_frag: 0

iet_tx_hold: 0

iet_tx_frag: 0

tx_mem_protect_err: 0

tx_pri0: 47

tx_pri1: 0

tx_pri2: 0

tx_pri3: 0

tx_pri4: 0

tx_pri5: 0

tx_pri6: 0

tx_pri7: 0

tx_pri0_bcnt: 10870

tx_pri1_bcnt: 0

tx_pri2_bcnt: 0

tx_pri3_bcnt: 0

tx_pri4_bcnt: 0

tx_pri5_bcnt: 0

tx_pri6_bcnt: 0

tx_pri7_bcnt: 0

tx_pri0_drop: 0

tx_pri1_drop: 0

tx_pri2_drop: 0

tx_pri3_drop: 0

tx_pri4_drop: 0

tx_pri5_drop: 0

tx_pri6_drop: 0

tx_pri7_drop: 0

tx_pri0_drop_bcnt: 0

tx_pri1_drop_bcnt: 0

tx_pri2_drop_bcnt: 0

tx_pri3_drop_bcnt: 0

tx_pri4_drop_bcnt: 0

tx_pri5_drop_bcnt: 0

tx_pri6_drop_bcnt: 0

tx_pri7_drop_bcnt: 0

And some relevant CPSW registers:

CTRL_MMR0 MCU_ENET_CTRL 0x40f04040 = 0x00000002 CPSW0_NUSS RGMII STATUS 0x46000018 = 0x00000000 CPSW0_NUSS PN_MAC_CONTROL 0x46022330 = 0x00000021 CPSW0_NUSS PN_MAC_STATUS 0x46022334 = 0xF0000008 STAT_0 (RXGOOD, TXGOOD) 0x4603a000 = 0x00000036 0x4603a034 = 0x00000000 STAT_1 (RXGOOD, TXGOOD) 0x4603a200 = 0x00000000 0x4603a234 = 0x00000036 STAT_0 (RXGOOD, TXGOOD) 0x4603a000 = 0x00000036 0x4603a034 = 0x00000000 STAT_1 (RXGOOD, TXGOOD) 0x4603a200 = 0x00000000 0x4603a234 = 0x00000036

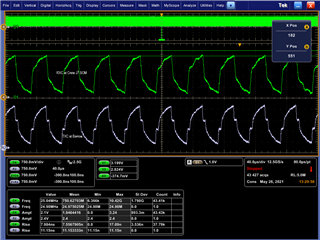

Besides the above, I've also confirmed with a scope that one SOM's RXC input is getting the remote SOM's TXC ouput, and the clock is the expected value for the above config: 100Mbps -> 25MHz TXC. (Ideally we want 1G, but I'm using 100M so I can use one of our cheap scopes at my desk)

I'm unsure what is wrong, though I am somewhat concerned about register CPSW_SS_RGMII_STATUS_REG (0x46000018) being 0x0?

Where next should I investigate?