Other Parts Discussed in Thread: SEGGER

Hi team,

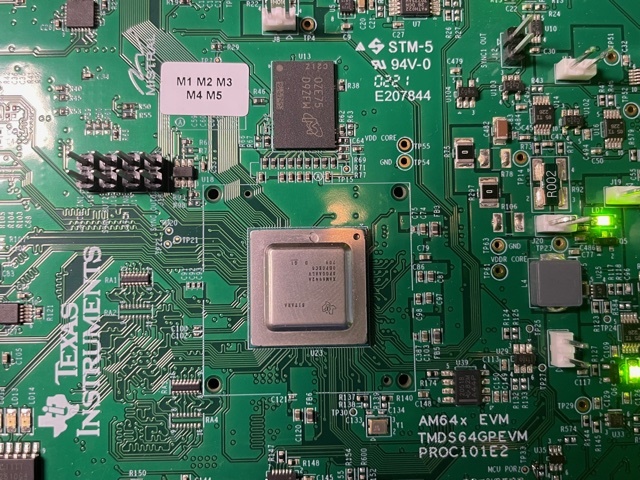

I could have connected r5f before.

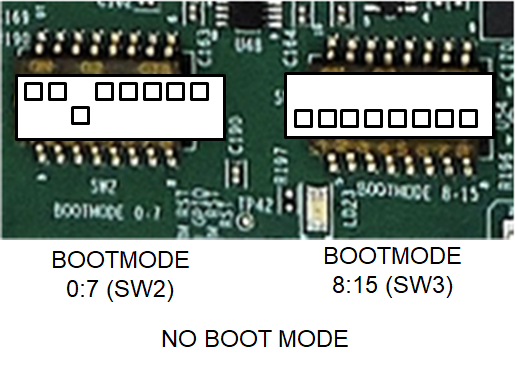

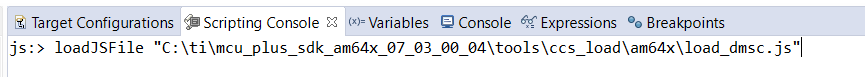

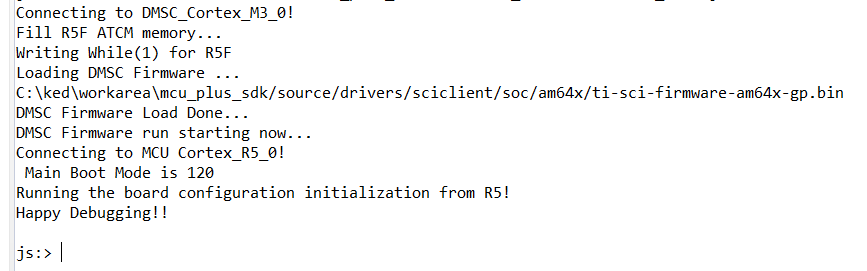

DDR initialization: run DDR initialization from the gel menu as shown below. I'm not sure if the initialization is finished, so I turn off the power and can't connect it later.

Please help to analyze it.thanks a lot.

Best regards,