Hi,

I was attempting to use a XDS560 to connect to a custom board with the TDA4VM using CCS 9.3.0.00012 .

When I do the "Test Connection", I get the following error:

[Start: Blackhawk XDS560v2-USB System Trace Emulator_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

/root/.ti/ccs930/0/0/BrdDat/testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 560/2xx-class product.

This utility will load the program 'libbh560v2u.out'.

Loaded FPGA Image: /root/ti/ccs930/ccs/ccs_base/common/uscif/./././././dtc_top.jbc

The library build date was 'Nov 25 2019'.

The library build time was '14:08:22'.

The library package version is '8.4.0.00006'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '6' (0x00000006).

The controller has an insertion length of '0' (0x00000000).

The cable+pod has a version number of '8' (0x00000008).

The cable+pod has a capability number of '7423' (0x00001cff).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the Nano-TBC VHDL.

The link is a 560-class second-generation-560 cable.

The software is configured for Nano-TBC VHDL features.

The controller will be software reset via its registers.

The controller has a logic ONE on its EMU[0] input pin.

The controller has a logic ONE on its EMU[1] input pin.

The controller will use falling-edge timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '2' (0x0002).

The utility logic has not previously detected a power-loss.

The utility logic is not currently detecting a power-loss.

Loaded FPGA Image: /root/ti/ccs930/ccs/ccs_base/common/uscif/./././././dtc_top.jbc

An error occurred while hard opening the controller.

-----[An error has occurred and this utility has aborted]--------------------

This error is generated by TI's USCIF driver or utilities.

The value is '-233' (0xffffff17).

The title is 'SC_ERR_PATH_BROKEN'.

The explanation is:

The JTAG IR and DR scan-paths cannot circulate bits, they may be broken.

An attempt to scan the JTAG scan-path has failed.

The target's JTAG scan-path appears to be broken

with a stuck-at-ones or stuck-at-zero fault.

[End: Blackhawk XDS560v2-USB System Trace Emulator_0]

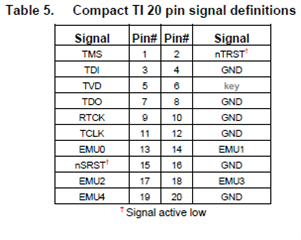

I'm sure my XDS560 Debug Probe is working as I've tested it on my J721e_evm board. The following is my schematic in which the TPs connect to TI_20 pins.

Please let me know what I can do to resolve the issue.

Thanks in advance.