Hello all,

I work with C6720 DSP and AIC23B audio codec (as slave) and I use the software demo "How to create delay based audio effects - spraaa5" from TI to control the codec.

After I adjust some registers in McASP init the SW works and I put audio signal into codec input through ADC - DAC and out to speakers. But the signals has little noise.

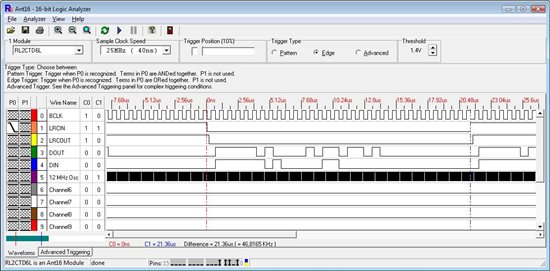

Then I checked the clocks and found out that the Clock ACLKX1 is too slow (should be 12 MHz to feed into BCLK of codec) - only 1.66 MHz:

I checked the registers of the clock stage and the HCLKXDIV is set to 1 so I measured 12 MHz at output pin AHCLKX pin with

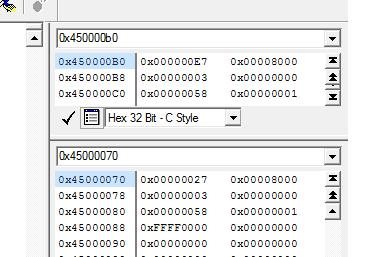

logic probe. I init the divider CLKXDIV to 1, but the ACLKX pin is 1.66 MHz and the memory registers show following:

The register is set to 0xE7 but I init with 0xE0. The devider value of 0x07 is correct for the 1.66 MHz. In memory window I changed the value to 0xE0 hard and measured the

clock ACLKX: Result: 12 MHz. In software I set all CLKXDIV bits to "0" - never changes. Then (for test) I set one of the higher register bits to "1" to check that the right register

is used: the register is OK.

This is the software init of McASP1 (I used McASP1 instead of the original McASP0 in spraaa5 code):

--------------------------------

// configuration of MCASP1

#define PADKDEMO_MCASP1_HWSETUP { \

/* Value to be loaded in global control register (GLBCTL) */ \

{ \

/* Pin function register (PFUNC) */ \

(0<< 0) /* AXR1_0: McASP1 */ \

| (0<< 1) /* AXR1_1: McASP1 */ \

| (0<< 2) /* AXR1_2: McASP1 */ \

| (0<< 3) /* AXR1_3: McASP1 */ \

| (0<< 27) /* AHCLKX1: McASP1 */ \

| (0<< 26) /* ACLKX1: McASP1 */ \

| (0<< 28) /* AFSX1: McASP1 */ \

| (0<< 31), /* AFSR1: McASP1 */ \

\

/* Pin direction register (PDIR) */ \

(1<<31) /* AFSR : Input */ \

| (1<<30) /* AHCLKR: OUTPUT */ \

| (1<<29) /* ACLKR : OUTPUT */ \

| (1<<28) /* AFSX : Output */ \

| (1<<27) /* AHCLKX: OUTPUT */ \

| (1<<26) /* ACLKX : Output */ \

| (1<<25) /* AMUTE : *unused */ \

| (0<<10) /* AXR10 : unused */ \

| (0<< 9) /* AXR9 : unused */ \

| (0<< 8) /* AXR8 : unused */ \

| (0<< 7) /* AXR7 : unused */ \

| (0<< 6) /* AXR6 : unused */ \

| (0<< 5) /* AXR5 : unused */ \

| (0<< 4) /* AXR4 : unused */ \

| (0<< 3) /* AXR3 : Input Codec 2 */ \

| (1<< 2) /* AXR2 : Output Codec 2 */ \

| (0<< 1) /* AXR1 : Input Codec 1 */ \

| (1<< 0), /* AXR0 : Output Codec 1 */ \

\

/* Global control register (GBLCTL) */ \

0x00000000, /* Everything in reset */ \

\

/* Decides whether McASP operates in DIT mode (DITCTL) */ \

0x00000000, /* DIT mode disable */ \

\

/* Digital loopback mode setup (DLBEN) */ \

0x00000000, /* Loopback mode disable */ \

\

/* Mute control register (AMUTE) */ \

0x00000000, /* AMUTE pin is disabled */ \

\

/* Setup serializer control register (SRCTL0-15) */ \

0x00000001, /* Serializer 0 is in tx Codec 1 */ \

0x00000002, /* Serializer 1 is in rx Codec 1 */ \

0x00000000, /* Serializer 2 is in tx Codec 2 */ \

0x00000000, /* Serializer 3 is in rx Codec 2 */ \

0x00000000, /* Serializer 4 is unused */ \

0x00000000, /* Serializer 5 is unused */ \

0x00000000, /* Serializer 6 is unused */ \

0x00000000, /* Serializer 7 is unused */ \

0x00000000, /* Serializer 8 is unused */ \

0x00000000, /* Serializer 9 is unused */ \

0x00000000, /* Serializer 10 is unused */ \

0x00000000, /* Serializer 11 is unused */ \

0x00000000, /* Serializer 12 is unused */ \

0x00000000, /* Serializer 13 is unused */ \

0x00000000, /* Serializer 14 is unused */ \

0x00000000 /* Serializer 15 is unused */ \

}, \

\

/* Receiver settings */ \

{ \

/* To mask or not to mask (RMASK) */ \

0xFFFFFFFF, /* 24-bits left justified */ \

\

/* Format details as per (RFMT) */ \

( 0<<16) /* XDATDLY: Transmit with 1 bit delay */ \

| ( 1<<15) /* XRVRS : MSB first */ \

| ( 0<< 3) /* XBUSSEL: Writes from dMAX port */ \

| (15<< 4) /* XSSZ : 32-bit slot size */ \

| ( 0<< 0), /* XROT : No rotation */ \

\

/* Configure the rcv frame sync (AFSRCTL) */ \

(2<< 7) /* RMOD : 2-slot TDM, I2S */ \

| (1<< 4) /* FRWID: Single word frame sync */ \

| (1<< 1) /* FSRM : Internally-generated tx frame sync */ \

| (0<< 0), /* FSRP : Start on falling edge */ \

\

/* Specifies which TDM slots are active (RTDM) */ \

0x00000003, /* Enable all slots */ \

\

/* Controls generation of McASP interrupts (RINTCTL) */ \

0x00000000, /* No interrupts */ \

\

/* Status register (controls writable fields of STAT reg) (RSTAT) */\

0x00000000, \

\

/* Event control register (REVTCTL) */ \

0x00000000, \

\

/* Clock settings for rcv */ \

{ \

/* Clock details (ACLKRCTL) */ \

(0<< 7) /* CLKRP : RX on rising edge */ \

| (1<< 6) /* ASYNC : TX and RX are asynchronous ? */ \

| (1<< 5) /* CLKRM : Int clk source from PLL div */ \

| (0<< 0), /* CLKRDIV: Need to be initialized by user */\

\

/* High clock details (AHCLKRCTL) */ \

(1<<15) /* HCLKRM : Clock intern */ \

| (0<<14) /* HCLKRP : Rising edge */ \

| (0<< 0), /* HCLKRDIV: AHCLKR = AUXCLK / 1 */ \

\

/* Config receive/transmit clock failure detection (RCLKCHK) */ \

0x00FF0000 /* Not used */ \

} \

}, \

\

/* Transmitter settings */ \

{ \

/* To mask or not to mask (XMASK) */ \

0xFFFFFFFF, /* 24-bits left justified */ \

\

/* Format details as per (XFMT) */ \

( 0<<16) /* XDATDLY: Transmit with 1 bit delay */ \

| ( 1<<15) /* XRVRS : MSB first */ \

| ( 0<< 3) /* XBUSSEL: Writes from dMAX port */ \

| (15<< 4) /* XSSZ : 32-bit slot size */ \

| ( 0<< 0), /* XROT : No rotation */ \

\

/* Configure the xmt frame sync (AFSXCTL) */ \

(2<< 7) /* XMOD : 2-slot TDM */ \

| (1<< 4) /* FXWID: Single word frame sync */ \

| (1<< 1) /* FSXM : Internally-generated tx frame sync */ \

| (0<< 0), /* FSXP : Start on rising edge */ \

\

/* Specifies which TDM slots are active (XTDM) */ \

0x00000003, /* Enable all slots */ \

\

/* Controls generation of McASP interrupts (XINTCTL) */ \

0x00000000, /* No interrupts */ \

\

/* Status register (controls writable fields of STAT reg) (XSTAT) */\

0x00000000, \

\

/* Event control register (XEVTCTL) */ \

0x00000000, \

\

/* Clock settings for xmt */ \

{ \

/* Clock details (ACLKXCTL) */ \

(1<< 7) /* CLKXP : TX on falling edge */ \

| (1<< 6) /* ASYNC : TX and RX are asynchronous ? */ \

| (1<< 5) /* CLKXM : Int clk source from PLL div */ \

| (0<< 0), /* CLKXDIV: Need to be initialized by user */\

\

/* High clock details (AHCLKXCTL) */ \

(1<<15) /* HCLKXM : Clock intern*/ \

| (0<<14) /* HCLKXP : Rising edge */ \

| (0<< 0), /* HCLKXDIV: AHCLKX = AUXCLK / 1 */ \

\

/* Conf receive/transmit clock failure detection (XCLKCHK) */ \

0x00FF0000 /* Not used */ \

} \

}, \

\

/* Power down emulation mode params - PWRDEMU */ \

CSL_MCASP_PWRDEMU_FREE_OFF \

}

// CSL McASP 0 Module

CSL_McaspHandle hMcasp1;

CSL_McaspObj MCASP1Obj;

CSL_McaspHwSetup MCASP1HwCfg = PADKDEMO_MCASP1_HWSETUP;

--------------------------------------------

What is wrong there? Can anybody help me? With software init I can never change the divider bits of CLKXDIV. Always the value of 7h.

Thanks and best regards,

Michael.