HI, CHAMPS:

SDK: Processor SDK RTOS J721E07_03_00

now i try on CAN Response and Bootloader Demo Application and attempt to boot linux following given descriptions:

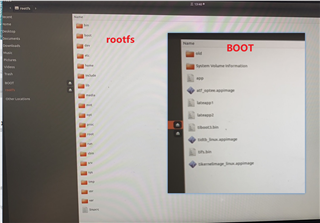

Writing needed binaries to MMCSD

To run the default TI RTOS applications on all the main domain cores, copy the following binaries onto the MMCSD card:

- coresdk_rtos_jacinto_xx_yy_xx_bb/pdk_jacinto_07.x.x/packages/ti/boot/sbl/binary/$board/cust/bin/sbl_mmcsd_img_mcu1_0_release.tiimage, rename to tiboot3.bin

- coresdk_rtos_jacinto_xx_yy_xx_bb/pdk_jacinto_07.x.x/packages/ti/drv/sciclient/soc/V1/tifs.bin (for J721E)

- coresdk_rtos_jacinto_xx_yy_xx_bb/mcusw/binary/can_boot_app_mcu_rtos/bin/$board/can_boot_app_mcu_rtos_mcu1_0_release.appimage, rename to app

- coresdk_rtos_jacinto_xx_yy_xx_bb/mcusw/mcuss_demos/boot_app_mcu_rtos/main_domain_apps/binary/bin/<board/multicore_MCU2_0_MCU2_1_stage1.appimage, rename to lateapp1

- J721E: coresdk_rtos_jacinto_xx_yy_xx_bb/mcusw/mcuss_demos/boot_app_mcu_rtos/main_domain_apps/binary/bin/<j721e_evm/multicore_DSPs_MCU3_0_MCU3_1_stage2.appimage, rename to lateapp2

To alternatively boot Linux on MPU1_0 (while still booting TI RTOS applications on the other main domain cores), also copy the following binaries onto the MMCSD card:

- coresdk_rtos_jacinto_xx_yy_xx_bb/mcusw/mcuss_demos/boot_app_mcu_rtos/main_domain_apps/binary/bin/$board/atf_optee.appimage

- coresdk_rtos_jacinto_xx_yy_xx_bb/mcusw/mcuss_demos/boot_app_mcu_rtos/main_domain_apps/binary/bin/$board/tidtb_linux.appimage

- coresdk_rtos_jacinto_xx_yy_xx_bb/mcusw/mcuss_demos/boot_app_mcu_rtos/main_domain_apps/binary/bin/$board/tikernelimage_linux.appimage

Note that, for Linux/QNX binaries, the can_boot_app_mcu_rtos_mcu1_0_release.appimage will also need to be rebuilt, as described in Creating HLOS appimages for Linux or QNX, and copied again to the MMCSD card. For booting the remaining MAIN domain cores (other than A72), you can simply reuse the RTOS images that were built in an earlier step in the binaries: "multicore_MCU2_0_MCU2_1_stage1.appimage" & "multicore_DSPs_MCU3_0_MCU3_1_stage2.appimage".

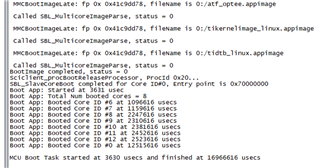

but output serial log shows me like this,

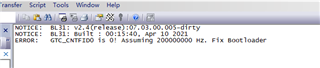

it says that GTC_CNTFID0 equals 0, i have no any clues why this happens , please help me to figure this out, many thx.