Hi team,

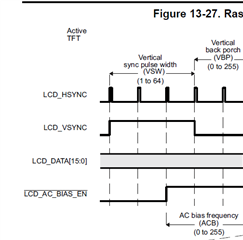

Figure13-27 in TRM shows VSYNC rising edges sync with HSYNC rising edges.

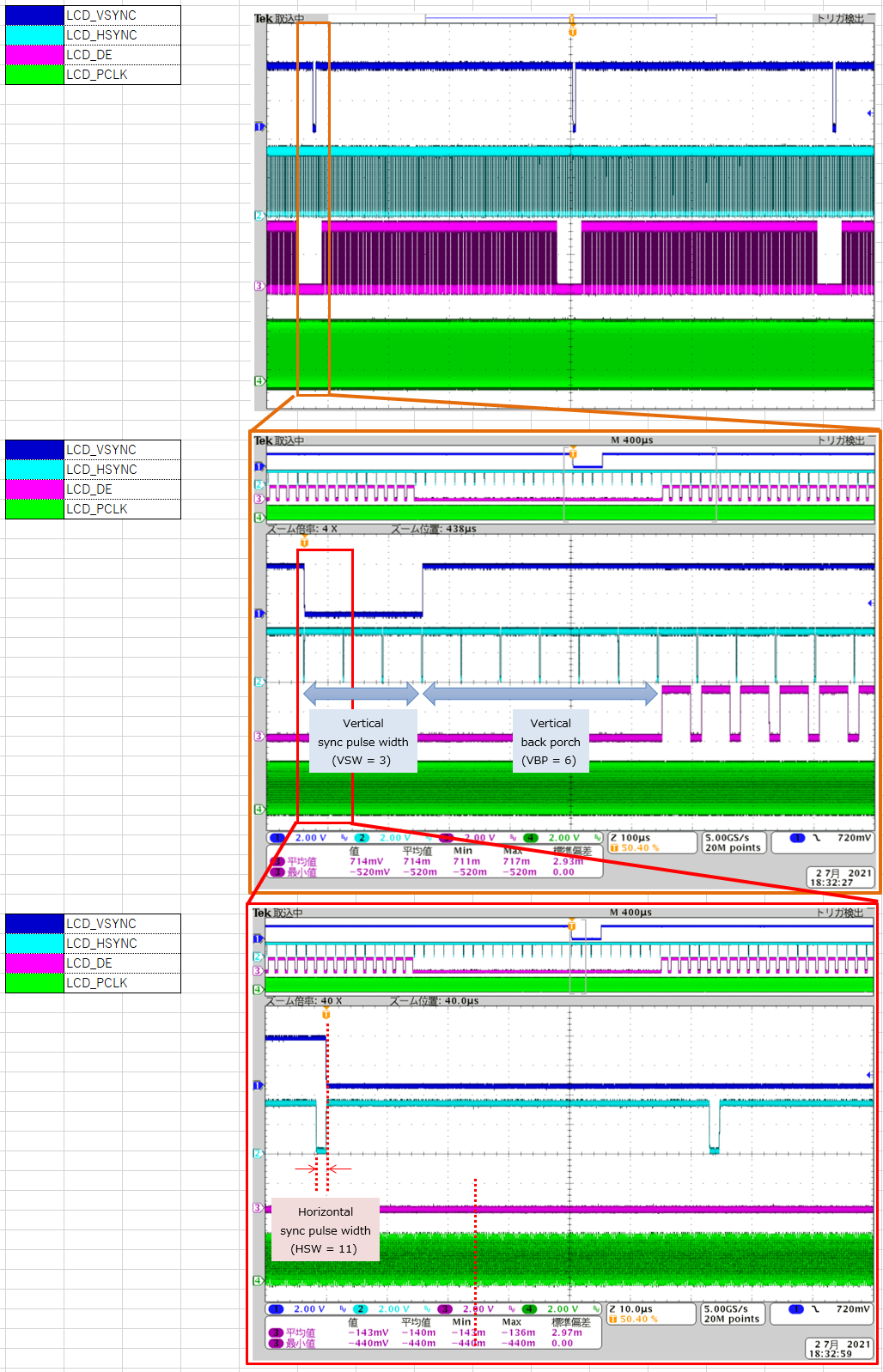

However, in our board, VSYNC falling edges sync with HSYNC rising edges. (We set invert flag for both VSYNC and HSYNC)

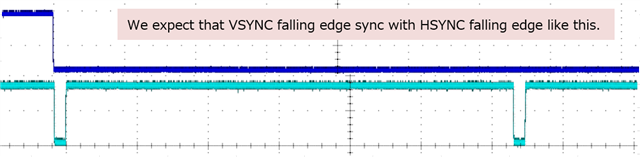

How can I align VSYNC falling edges to HSYNC falling edges?

Best Regards,

Junpei Kishi