Hi Team,

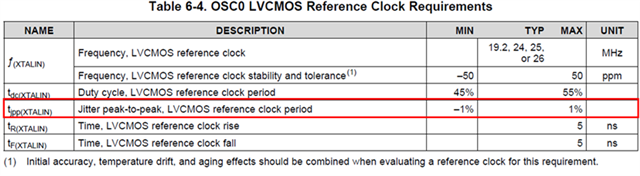

Jitter peak-to-peak is defined in the data sheet by the red border as below.

My customer would like to have a graphic representation of the TI-defined Jitter peak-to-peak.

Do you have any document for it?

Would you please explain What is TI-definition for this parameter?

How to calculate it?

Would you also tell me what the impact might be if tjpp(XTALIN) cannot be satisfied?

Thanks and Best regards,

Kuerbis