Other Parts Discussed in Thread: TPS65217

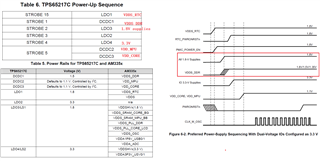

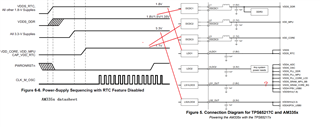

I compared Powering the AM335x with the TPS65217x . (Rev. I) with AM335x datasheet power sequence, found LDO3(1.8V) and DCDC1(1.5V) sequence of TPS65217C doesn't meet AM335x requirement. which is right? Beaglebone Black follow document of powering the AM335x with the TPS65217x design.