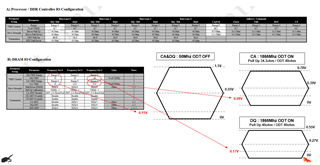

On our own TDA4vm board, we used samsung or SK hynix LPDDR4 chip, but during sbl boot process

it halt during DDR clock changing handshake, and the log is as below, this does not happen every time, and the fail rate is not steady

for some boards it works well, but for some boards it fails sometimes, please help to clarify the resason, thanks

Failed to set voltage to 800 mV for Slave:0x48, Res:0x0

Initlialzing PLLs ...Failed to set the PLL clock freq at index =2

Failed to set the PLL clock freq at index =17

Failed to set the PLL clock freq at index =19

Failed to set the PLL clock freq at index =20

Failed to set the PLL clock freq at index =21

Failed to set the PLL clock freq at index =22

Failed to set the PLL clock freq at index =23

Failed to set the PLL clock freq at index =24

done.

InitlialzingClocks ...done.

version hy 0001

Initlialzing DDR ...Board_DDRProbe: PASS

Board_DDRInitDrv: PASS

--->>> LPDDR4 Initialization is in progress ... <<<---

Reg Value: 128

Frequency Change type 1 request from Controller

Reg Value: 0

Reg Value: 128

Frequency Change type 0 request from Controller

Reg Value: 0

Reg Value: 128

Frequency Change type 1 request from Controller

Reg Value: 0

Reg Value: 0

Reg Value: 0