Part Number: TMDSIDK574

Hi Everyone,

I want to configure PWMSS1 based on time for AM5749 processor. For that i have referred AM5749 Technical Reference Manual section 30. I want to configure gpio4_0 as an epwm. So for that with some reference i have configure as per the attached file(pwm.c and pwm.h)

/**

* main.c

*/

#include "pwm.h"

CSL_EpwmAqActionCfg_t aqctrla = {AQ_NO_ACTION, AQ_CLEAR, AQ_TOGGLE, AQ_NO_ACTION, AQ_NO_ACTION, AQ_NO_ACTION};

/* Function to setup PWM module one-time configurations */

static void BoardDiag_pwmInit(uint32_t pwmssBaseAddr)

{

/*Time base clock configuring using prescaler*/

CSL_epwmTbTimebaseClkCfg(pwmssBaseAddr, TBCLK_FREQ, MODULE_CLK);

/*Clearing phase and direction set to count up*/

CSL_epwmTbSyncEnable(pwmssBaseAddr, CLEAR_PHASE_REG, TB_COUNT_UP);

/*Disabling the Sync*/

CSL_epwmTbSyncDisable(pwmssBaseAddr);

/*Configuring the EPWM_AQCTLA register*/

CSL_epwmAqActionOnOutputCfg(pwmssBaseAddr, CSL_EPWM_OUTPUT_CH_A, &aqctrla);

}

/* Function to configure PWM pulse generation */

static void BoardDiag_pwmConfig(uint32_t pwmssBaseAddr, float dutyCycle)

{

float period = TBCLK_FREQ/PWM_FREQ;

/* This is the compare count value to be configured to

* generate the requested dutyCycle.

*/

uint32_t cmpCntVal = (period - (uint32_t)(period * (dutyCycle/100)));

/* PWM pulse frequency configuration */

CSL_epwmTbPwmFreqCfg(pwmssBaseAddr, TBCLK_FREQ, PWM_FREQ, TB_COUNT_UP,

TB_IMMEDIATE);

/* Configuring EPWM_CMPCTL register */

CSL_epwmCounterComparatorCfg(pwmssBaseAddr, CSL_EPWM_CC_CMP_A,

cmpCntVal, CC_SHADOW,

CC_CTR_ZERO, OVER_WRITE_SHADOW_DISABLED);

/* Resetting the counter */

CSL_epwmTbWriteTbCount(pwmssBaseAddr, RESET_TB_COUNT_VALUE);

}

/* Enables clock for PWM module */

static void BoardDiag_pwmClockConfig(void)

{

#if defined(evmAM335x)

/* Enable PRCM for PWMSS0 */

HW_WR_REG32((SOC_CM_PER_REGS + CM_PER_EPWMSS0_CLKCTRL), 0x02);

/* Enable the PWM clock using the PMWSS0 CLKCONFIG Register*/

HW_WR_REG32((PWM_BASE_ADDRESS + PWMSS_CLKCONFIG), 0x100);

/* Time base clock for PWMSS1 module */

HW_WR_REG32((SOC_CONTROL_REGS + CONTROL_PWMSS_CTRL), 0x1);

#elif defined(evmAM572x)

/* Enable PRCM for PWMSS2 */

HW_WR_REG32(SOC_L4PER_CM_CORE_BASE + CM_L4PER2_PWMSS2_CLKCTRL, 0x2);

while ((HW_RD_REG32(SOC_L4PER_CM_CORE_BASE +

CM_L4PER2_PWMSS2_CLKCTRL) & (0x00030000)) != 0x0);

/* Time base clock for PWMSS2 module */

HW_WR_FIELD32(SOC_CTRL_MODULE_CORE_CORE_REGISTERS_BASE +

CTRL_CORE_CONTROL_IO_2,

CTRL_CORE_CONTROL_IO_2_PWMSS2_TBCLKEN, 1);

#elif defined(evmK2G)

/* Time base clock enable for EHRPWM_3 module */

HW_WR_REG32((CSL_BOOT_CFG_REGS + BOOTCFG_EPWM_CTL_REG_OFFSET), 0x08);

#elif defined(idkAM437x)

/* Enabling the pwm clock for the PWMSS2 module */

HW_WR_REG32(PWM_BASE_ADDRESS + PWMSS_CLKCONFIG, 0x100);

/*Enabling the Time-base clock for the PWMMSS2 module */

HW_WR_REG32(SOC_CONTROL_MODULE_REG + CTRL_PWMSS, 0x4);

#elif defined(custom_board)

/* Enable PRCM for PWMSS1 */

HW_WR_REG32(SOC_L4PER_CM_CORE_BASE + CM_L4PER2_PWMSS1_CLKCTRL, 0x2);

while ((HW_RD_REG32(SOC_L4PER_CM_CORE_BASE +

CM_L4PER2_PWMSS1_CLKCTRL) & (0x00030000)) != 0x0);

/* Time base clock for PWMSS1 module */

HW_WR_FIELD32(SOC_CTRL_MODULE_CORE_CORE_REGISTERS_BASE +

CTRL_CORE_CONTROL_IO_2,

CTRL_CORE_CONTROL_IO_2_PWMSS1_TBCLKEN, 1);

#endif

}

/* Configures pinmux for PWM module */

static void BoardDiag_pwmPinmuxConfig(void)

{

uint32_t regVal;

#if defined(evmAM335x)

regVal = HW_RD_REG32(SOC_CONTROL_REGS + CONTROL_CONF_SPI0_SCLK);

regVal = ((regVal & ~0x07) | 0x03);

HW_WR_REG32(SOC_CONTROL_REGS + CONTROL_CONF_SPI0_SCLK, regVal);

#elif defined(evmAM572x)

// regVal = HW_RD_REG32(CTRL_CORE_PAD_GPIO6_10_ADDR);

regVal = HW_RD_REG32(0x374U);

regVal = ((regVal & ~0x0F) | 0x0A);

// HW_WR_REG32(CTRL_CORE_PAD_GPIO6_10_ADDR, regVal);

HW_WR_REG32(0x374U, regVal);

#elif defined(evmK2G)

regVal = HW_RD_REG32(CSL_BOOT_CFG_REGS + BOOTCFG_PAD_CONFIG_REG_73_OFFSET);

regVal = ((regVal & ~0x0F) | 0x04);

HW_WR_REG32(CSL_BOOT_CFG_REGS + BOOTCFG_PAD_CONFIG_REG_73_OFFSET, regVal);

#elif defined(idkAM437x)

regVal = HW_RD_REG32(SOC_CONTROL_MODULE_REG + CTRL_CONF_GPMC_AD8);

regVal = ((regVal & ~0x0F) | 0x04);

HW_WR_REG32(SOC_CONTROL_MODULE_REG + CTRL_CONF_GPMC_AD8, regVal);

#elif defined(custom_board)

regVal = HW_RD_REG32(0x364U);

regVal = ((regVal & ~0x0F) | 0x0A);

HW_WR_REG32(0x364U, regVal);

#endif

}

/* Function to generate delay */

static void BoardDiag_pwmAppDelay(uint32_t delay)

{

volatile uint32_t cnt = 0;

while(cnt < delay)

{

asm("");

cnt++;

}

}

int main(void)

{

uint8_t dutyCycle;

Board_initCfg boardCfg;

#ifdef PDK_RAW_BOOT

boardCfg = BOARD_INIT_MODULE_CLOCK |

BOARD_INIT_PINMUX_CONFIG |

BOARD_INIT_UART_STDIO;

#else

// boardCfg = BOARD_INIT_UART_STDIO;

boardCfg = BOARD_INIT_PINMUX_CONFIG | BOARD_INIT_MODULE_CLOCK | BOARD_INIT_UART_STDIO;

#endif

Board_init(boardCfg);

UART_printf("\n*********************************************\n");

UART_printf("* PWM Test *\n");

UART_printf("*********************************************\n");

BoardDiag_pwmClockConfig();

BoardDiag_pwmPinmuxConfig();

BoardDiag_pwmInit(0x4843e000U);

/* Configures PWM for different duty cycles */

for(dutyCycle = 25; dutyCycle <= 75; dutyCycle += 25)

{

UART_printf("\nGenerating %dKHz PWM pulse with %d Duty Cycle\n", PWM_FREQ/1000, dutyCycle);

BoardDiag_pwmConfig(PWM_BASE_ADDRESS, dutyCycle);

BoardDiag_pwmAppDelay(DELAY);

}

/* Reset the duty cycle to 50% */

BoardDiag_pwmConfig(PWM_BASE_ADDRESS, 50);

UART_printf("\nPWM Test Completed!\n");

/* Restore the default pin mux since the pin mux is changed for PWM */

boardCfg = BOARD_INIT_PINMUX_CONFIG;

Board_init(boardCfg);

return 0;

}

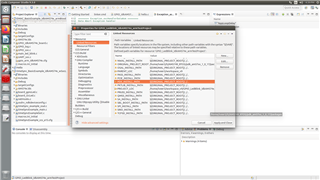

While building the code i was getting error in the file of csl_epwm.h.I have observed that location of csl_epwm.h is at C:\ti\AM5749\pdk_am57xx_1_0_17\packages\ti\csl. and its source file csl_epwm.c location is at C:\ti\AM5749\pdk_am57xx_1_0_17\packages\ti\csl\src\ip\epwm\V0\priv .

At that time i was getting error as an undefined function for all csl function like CSL_epwmTbTimebaseClkCfg

Then i have shifted these files

csl_epwm.c

csl_epwm.h

cslr_epwm.h

hw_pwmss_epwm.h

hw_pwmss_submodule_offsets.h

to Project\Include

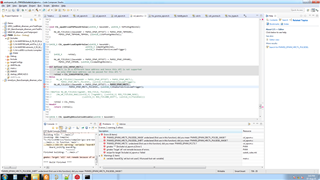

After that it is giving me error in the HW_WR_FIELD16 as per the attached image

I have following query

1) Does the directory of csl_epwm.h is correct, at C:\ti\AM5749\pdk_am57xx_1_0_17\packages\ti\csl.

2) Whatever method i am following is correct?

3) How to configure ePWM for AM5749 processor?

Thanks & Regards,

Divyesh Patel