Part Number: AM6548

Other Parts Discussed in Thread: TPS54618, TPS62827,

Hi all,

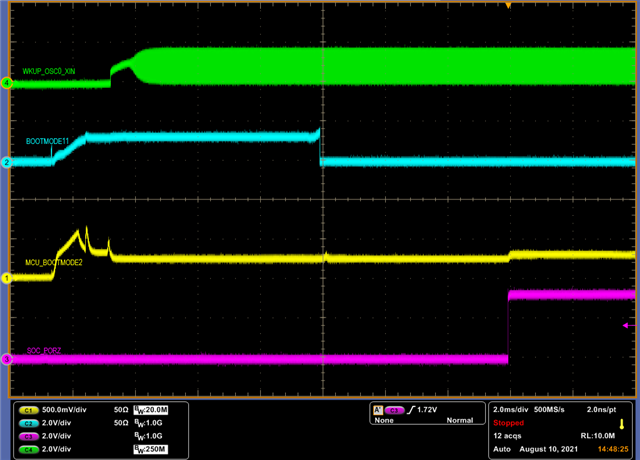

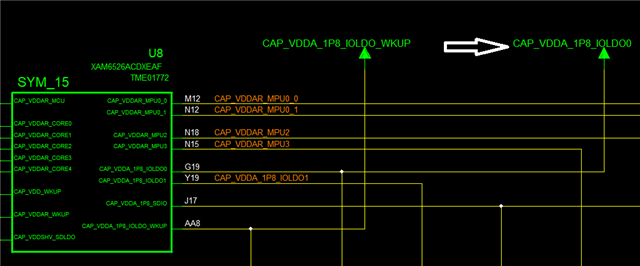

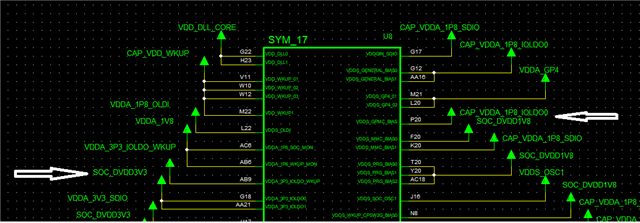

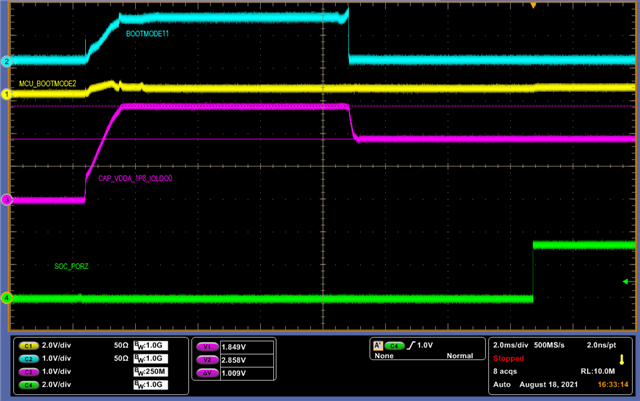

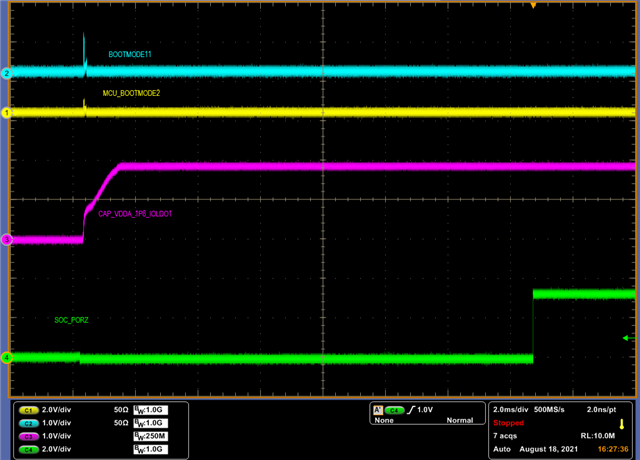

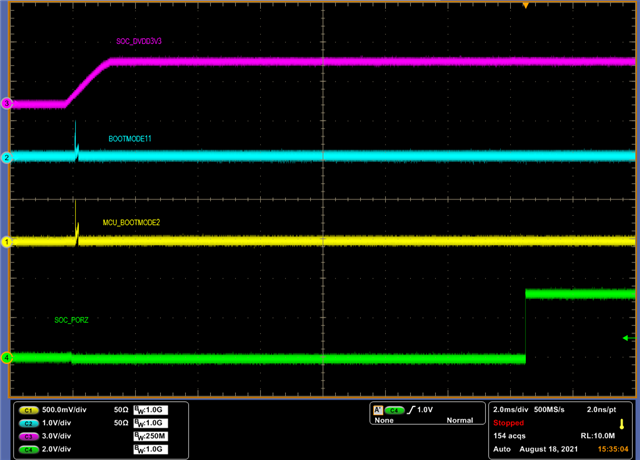

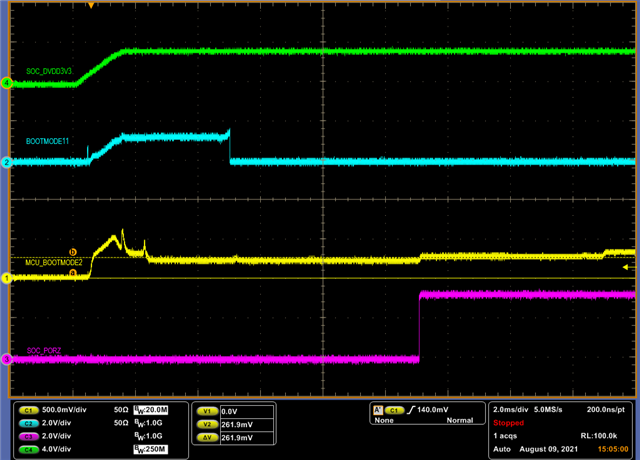

During the HW verification process of our board with the X6580AACD device, we have noticed a strange behavior of BOOTMODE and MCU_BOOTMODE pins. The screen snapshot of measurement is presented below:

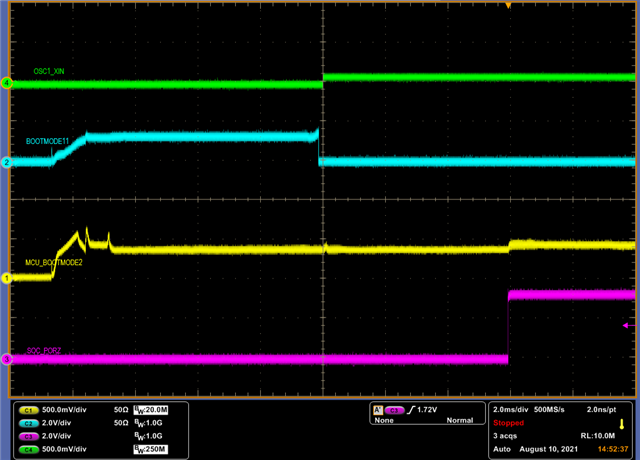

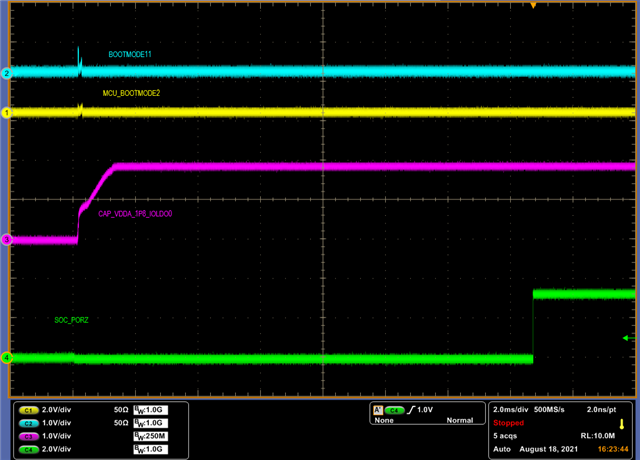

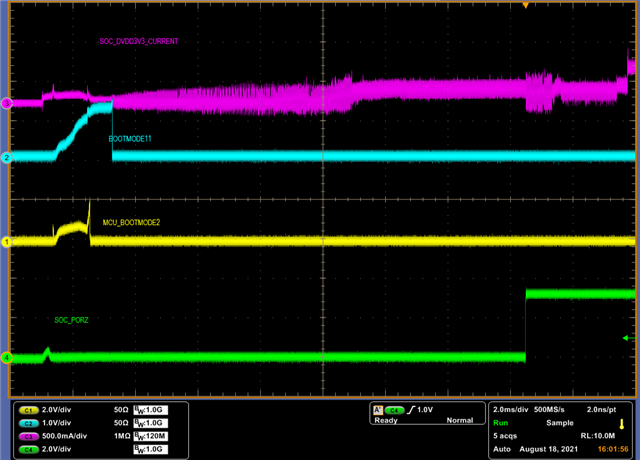

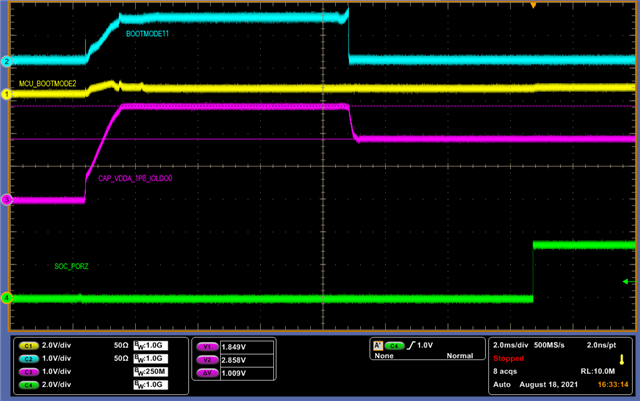

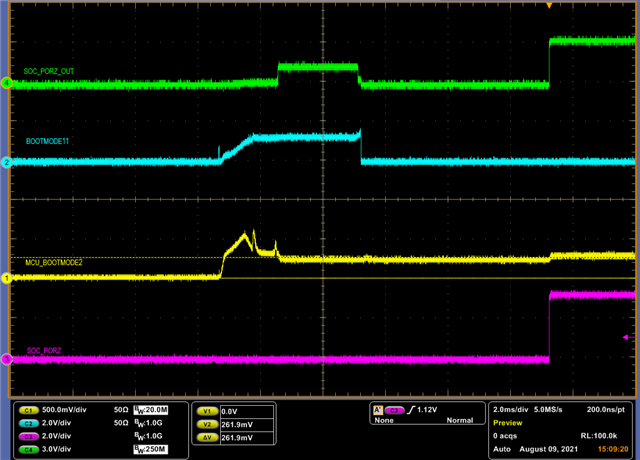

MCU_BOOTMODE2 and BOOTMODE11 are selected since they are pulled down with resistors of 100K (the same resistors were used in our previous version of PCB with X6580ACD device and on IDK board as well). The screen snapshot of the same measurement with SOC_PORZ_OUT signal is presented below:

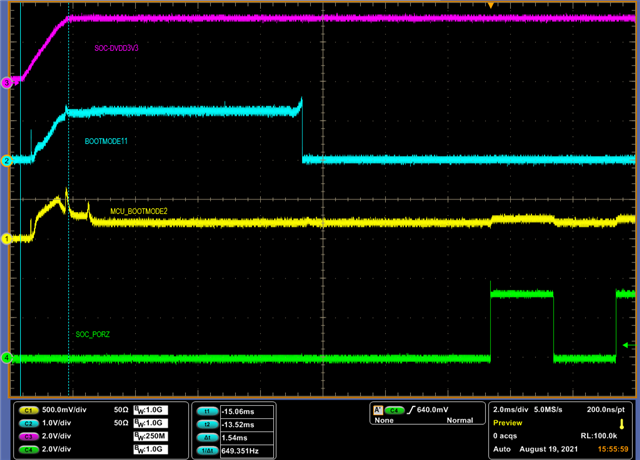

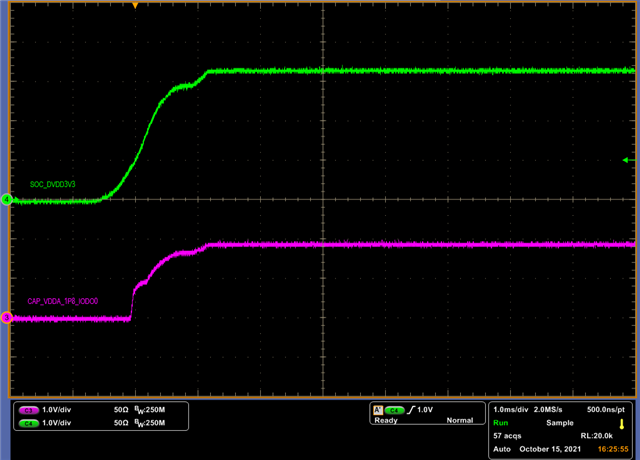

From previous snapshots, it can be seen that, for some reason, it seems that internal pull-up resistors on MCU_BOOTMODE pins remain active during the SOC_PORZ signal active state which is not expected according to the datasheet.

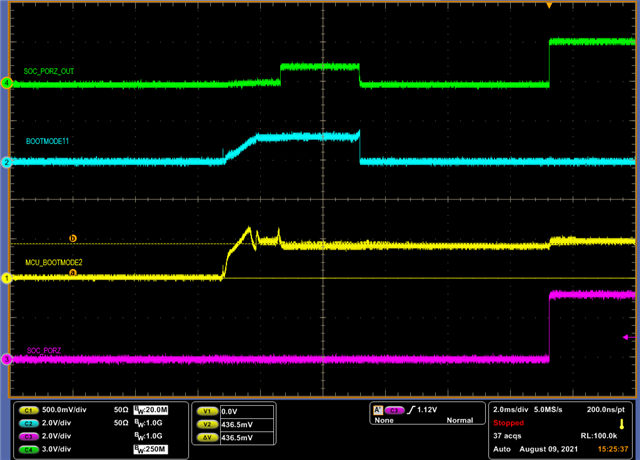

As Sitara SoC starts to heat up the voltage level on the MCU_BOOTMODE pins starts to rise to reach more than 500mV.

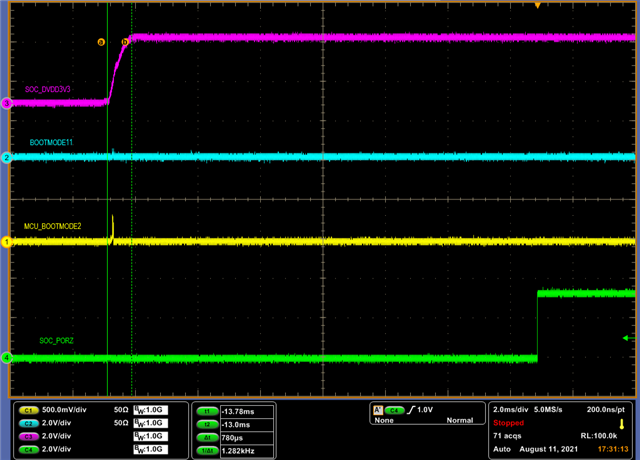

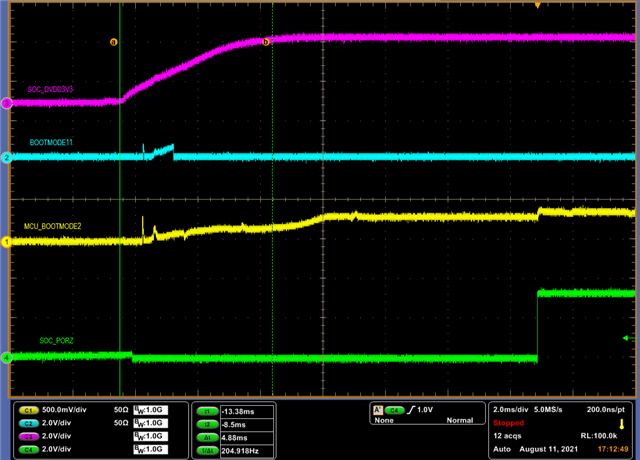

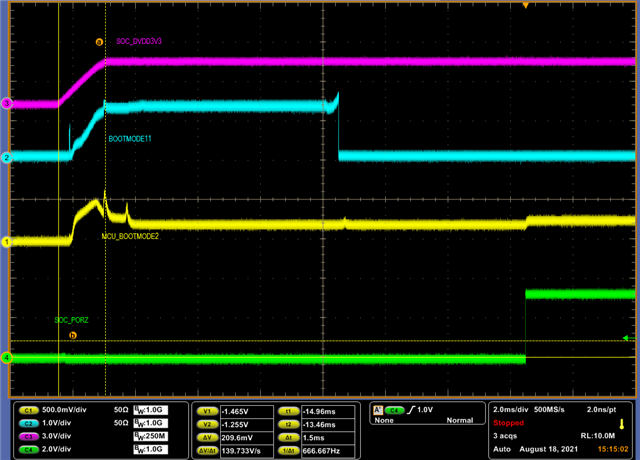

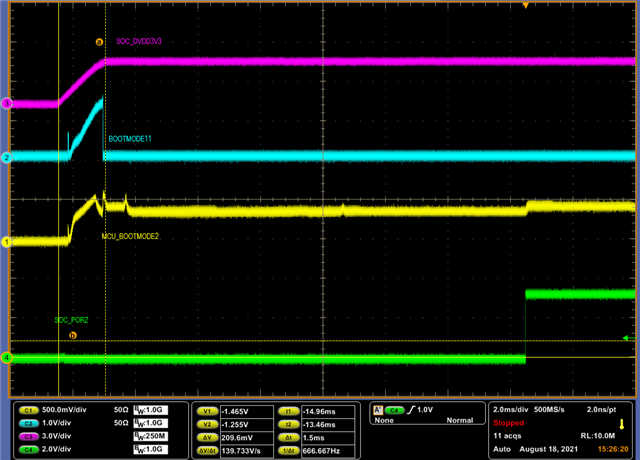

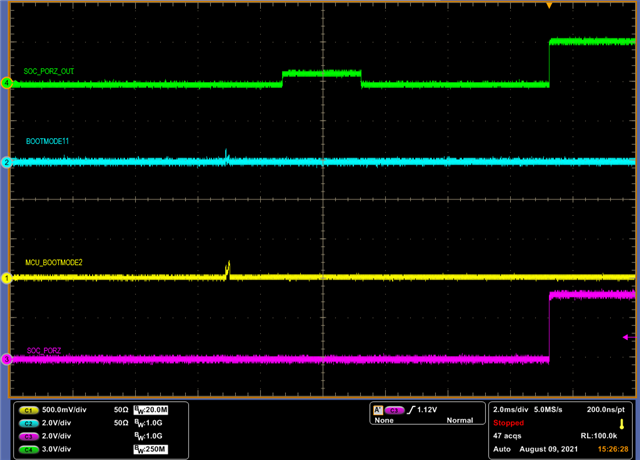

At some point, after additional heating, the MCU_BOOTMODE pins, as well as BOOTMODE pins start to behave normally:

As a result, on some boards, the wrong boot mode was selected. For example, since MCU_BOOTMODE2 is responsible for selecting reference clock logic 1 is selected instead of logic 0 (No PLL Configuration Done (slow speed backup) instead of 25MHz reference clock).

In our reset configuration, MCU_PORZ and PORZ pins are connected together, the MCU_BYP_POR signal is pulled high and PORZ_OUT and MCU_PORZ_OUT are pulled low by two resistors.

Just to mention, on the previous version of our board with the X6580ACD device and identical reset configuration the BOOTMODE and MCU_BOOTMODE pins are behaving properly.

My question is what can be done to prevent this Boot mode pins behavior? Also, is there some explanation for what we are measuring?

Best regards,

Zoran Dukic