Hi TI Team,

I have a question related to how to calculate the AUXCLK value for TDA2PXEVM McASP module.

I am trying to use the McASP transmit example provided in the CSL folder in the pdk:

~/PROCESSOR_SDK_VISION_03_08_00_00/ti_components/drivers/pdk_01_10_04_05/packages/ti/csl/example/mcasp/mcasp_transmit

I reviewed the TDA2Px Technical Reference Manual, and the following steps I used to figure out how to calculate the AUXCLK.

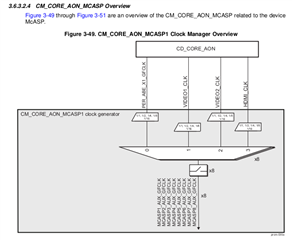

1. from "3.6.3.2.4 CM_CORE_AON_MCASP Overview", I can see the different possible sources of the McASP3_AUX_GFCLK and by reading the "CM_L4PER2_MCASP3_CLKCTRL[23:22] CLKSEL_AUX_CLK" (value 0) register, I can confirm that the "PER_ABE_X1_GFCLK" source is used.

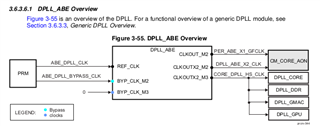

2. from "3.6.3.6.1 DPLL_ABE Overview", I can see that the "PER_ABE_X1_GFCLK" signal source is "ABE_DPLL_CLK" signal after passing the "DPLL_ABE" module.

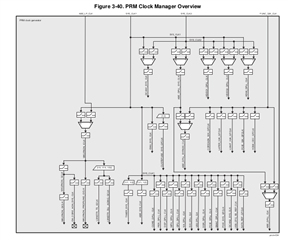

3. from "Figure 3-40. PRM Clock Manager Overview", I can see the different possible sources of the "ABE_DPLL_CLK" and by reading the "CM_CLKSEL_ABE_PLL_REF[0] CLKSEL" (value 0) and "CM_CLKSEL_ABE_PLL_SYS[0] CLKSEL" (value 1) register, I can confirm that the "SYS_CLK2" source is used.

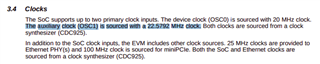

4. from "TDA2Px-ACD CPU EVM Board User's Guide" section "3.4 Clocks", The auxiliary clock (OSC1) is sourced with a 22.5792 MHz clock.

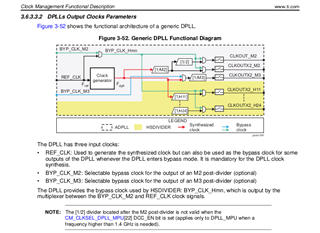

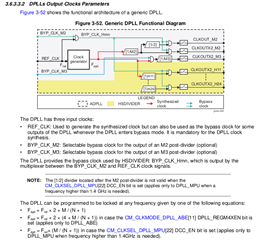

5. back to the "DPLL_ABE module", section "3.6.3.3.2 DPLLs Output Clocks Parameters" describes the calcution of the "PER_ABE_X1_GFCLK" output signal from "ABE_DPLL_CLK" input signal.

This depends on the M, N and M2 values besides the CM_CLKMODE_DPLL_ABE[11] DPLL_REGM4XEN.

these values are as follows:

M "CM_CLKSEL_DPLL_ABE[18:8] DPLL_MULT", is 200

N "CM_CLKSEL_DPLL_ABE[6:0] DPLL_DIV", is 9

CM_CLKMODE_DPLL_ABE[11] DPLL_REGM4XEN, is 0

M2 "CM_DIV_M2_DPLL_ABE[4:0] DIVHS", is 1

So, if I applied all the above sources, I can get that the AUXCLK equals to 451.584 MHz.

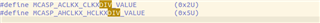

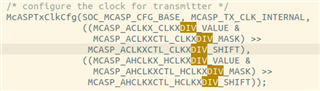

back to the "mcasp_transmit" example, it claims that the bit clock should be 10MHz by using "CLKXDIV" value 2 which results in value 3 and "HCLKXDIV" value 5 which results in value 6.

if the AUXCLK equals 451.584 MHz, and CLKXDIV" value 2 and "HCLKXDIV" value 5 , the bit clock should be 25.088 MHz not 10MHz as claimed

I need your help to figure out why my calculations does not match the claimed value as I will depend on these calculations for my application.

your input is highly appreciated.

Best regards,

Ahmed