Hi,

My customer is now evaluating their own board based on AM5706, but they found that the bus error occurred when GPMC accessed FROM. (The connected ICE was frozen.)

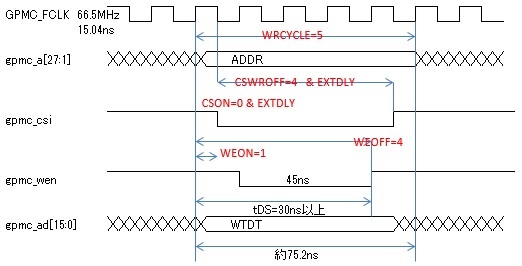

They’re using the CS0 area of GPMC and the asynchronous mode (No external wait) with Non-mux data and address. The GPMC internal clock is 66.5MHz, and it’s controlled by the timing like below, but the bus error occurred.

Do you know the cause why the error occurred ?

The GPMC timings are set as follows;

GPMC_CONFIG1_0:0x00001000

GPMC_CONFIG2_0:0x00040980

GPMC_CONFIG4_0:0x04010983

GPMC_CONFIG5_0:0x0008050A

GPMC_CONFIG6_0:0x0F070000

GPMC_CONFIG7_0:0x00000848

The access timing wave could be monitored during write access issue like the above figure. (CS and WE are verified.)

However, the ICE was frozen after that.

Note :

There is no issue on the read access.

If GPMC_CONFIG5_0:0x0008070A (WRCYCLETIME = 7), no error occurs. In the case of WRCYCLETIME=6, it’s frozen too.

Is there any relation with this ? or any restriction ?

Thanks and regards,

Hideaki