Hi,

We are trying to debug our custom board with AM4378 with XDS200 JTAG probe, we define target configuration as follows:

Debug probe is successfully detected and can debug, logs about it as follows:

[Start: Texas Instruments XDS2xx USB Debug Probe_0]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\utkuuy\AppData\Local\TEXASI~1\CCS\

ccs1030\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 560/2xx-class product.

This utility will load the program 'xds2xxu.out'.

The library build date was 'Jan 31 2021'.

The library build time was '19:18:41'.

The library package version is '9.3.0.00042'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '13' (0x0000000d).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

This emulator does not create a reset log-file.

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End: Texas Instruments XDS2xx USB Debug Probe_0]

[Start: Texas Instruments XDS2xx USB Debug Probe_1]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\utkuuy\AppData\Local\TEXASI~1\CCS\

ccs1030\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 560/2xx-class product.

This utility will load the program 'xds2xxu.out'.

The library build date was 'Jan 31 2021'.

The library build time was '19:18:41'.

The library package version is '9.3.0.00042'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '13' (0x0000000d).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

This emulator does not create a reset log-file.

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End: Texas Instruments XDS2xx USB Debug Probe_1]

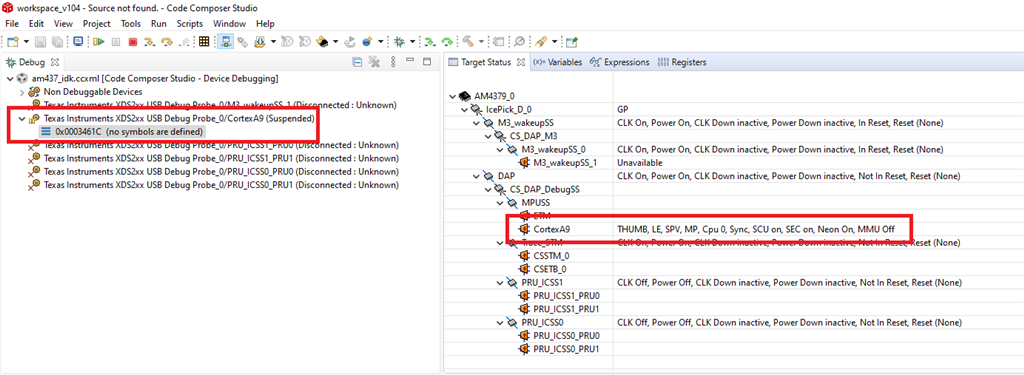

But when we try to connect the A9 core an error occurs, here is the error log:

Error connecting to the target:

(Error -1170 @ 0x0)

Unable to access the DAP. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK).

(Emulation package 9.3.0.00042)

Note: We tried to lower the TCLK but it didn't work.

Do we need to configure extra things or upload an extra file? Do you have an idea about the problem that we've faced with?

Schematic's part:

(We've tried remove or insert pull-up/pull-downs exactly same with EVM's with CTI header connections but we still get the same error.)