Other Parts Discussed in Thread: PCM1808

In SPRUH79C 23.0.21.3 Frame Sync Generator,It says:

-------------------------

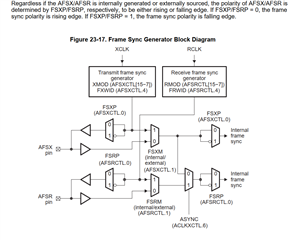

Regardless if the AFSX/AFSR is internally generated or externally sourced, the polarity of AFSX/AFSR is

determined by FSXP/FSRP, respectively, to be either rising or falling edge. If FSXP/FSRP = 0, the frame

sync polarity is rising edge. If FSXP/FSRP = 1, the frame sync polarity is falling edge.

-------------------------

If the AFSR polarity is a falling edge, as in the I2S format, set the FSRP bit to 1.

At this time, if FSRM = 1, "Internal frame sync" will fall at the beginning of the frame.

On the other hand, if FSRM = 0, "Internal frame sync" will rise at the beginning of the frame.

This behavior is considered to be inconsistent with the comments above.