Other Parts Discussed in Thread: AM5728, CODECOMPOSER, AM5718

We can't boot both DSP core and ARM A15 core of AM5706 with the same software of AM5728.

Are there anythings need change in AM5728 software?

This is customer board and customer software which works for AM5728 very well.

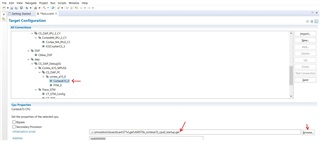

For DSP core, using Code Composer v930, ti_processor_sdk_rtos_am57xx_6_03_00_106.

For ARM A15, using WIndriver Workbench 4, VxWorks 7 RTOS.

Thanks.