Other Parts Discussed in Thread: TCA6424,

Hi, I want to use cpsw9g port 5 to connect with bcm89881 by RGMII.

but when the system bring up,and after i run the vision_apps_init.sh, the "GenericPhy_reset" function will be called all the time.

i'm sure the reason is that "while (hMcm->timerTaskShutDownFlag != true)" this conditions is always be true, which located at enet_mcm.c, in "EnetMcm_periodicTick" function.

but i don't kown why ???????

My SDK version: ti-processor-sdk-rtos-j721e-evm-07_03_00_07

My PDK version: pdk_jacinto_07_03_00_29

My Cpsw9g ports config as below :

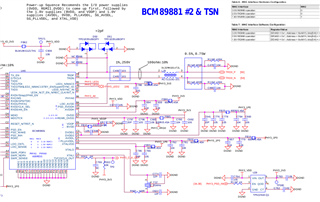

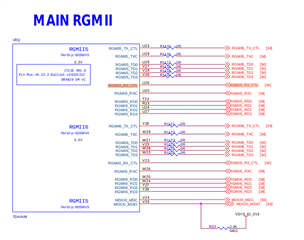

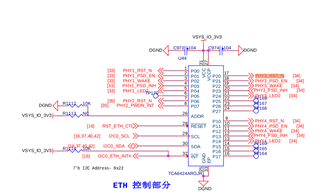

RGMII3 --> BCM89881

RGMII5 --> BCM89881

RGMII6 --> BCM89881

RGMII1 --> DP83867

My test data path is TDA4 --> CPSW9G -->RGMII5 --> BCM89881 --> T1 --> T1toRJ45 siwtch --> PC;

I will provide the hardware schematic later。

When the system bringup, run the vision_apps_init.sh ,the log is below:

root@j7-evm:~# root@j7-evm:~# cd /opt/vision_apps root@j7-evm:/opt/vision_apps# source ./vision_apps_init.sh root@j7-evm:/opt/vision_apps# [MCU2_0] 3.444721 s: CIO: Init ... Done !!! [MCU2_0] 3.444790 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz> [MCU2_0] 3.444830 s: APP: Init ... !!! [MCU2_0] 3.444848 s: SCICLIENT: Init ... !!! [MCU2_0] 3.445037 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla] [MCU2_0] 3.445071 s: SCICLIENT: DMSC FW revision 0x15 [MCU2_0] 3.445093 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU2_0] 3.445115 s: SCICLIENT: Init ... Done !!! [MCU2_0] 3.445136 s: UDMA: Init ... !!! [MCU2_0] 3.446187 s: UDMA: Init ... Done !!! [MCU2_0] 3.446238 s: MEM: Init ... !!! [MCU2_0] 3.446271 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e1000000 of size 16777216 bytes !!! [MCU2_0] 3.446324 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 3600000 of size 131072 bytes !!! [MCU2_0] 3.446369 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000000) @ d8000000 of size 16777216 bytes !!! [MCU2_0] 3.446413 s: MEM: Init ... Done !!! [MCU2_0] 3.446432 s: IPC: Init ... !!! [MCU2_0] 3.446460 s: IPC: 6 CPUs participating in IPC !!! [MCU2_0] 3.446493 s: IPC: Waiting for HLOS to be ready ... !!! [MCU2_0] 30.893546 s: IPC: HLOS is ready !!! [MCU2_0] 30.899093 s: IPC: Init ... Done !!! [MCU2_0] 30.899154 s: APP: Syncing with 5 CPUs ... !!! [MCU2_0] 30.917895 s: APP: Syncing with 5 CPUs ... Done !!! [MCU2_0] 30.918062 s: REMOTE_SERVICE: Init ... !!! [MCU2_0] 30.919871 s: REMOTE_SERVICE: Init ... Done !!! [MCU2_0] 30.919932 s: ETHFW: Init ... !!! [MCU2_0] 30.940989 s: CPSW_9G Test on MAIN NAVSS [MCU2_0] 30.952818 s: [LXC] phyCfg->phyAddr = 12, portNum = 0 [MCU2_0] 30.952875 s: [untouch:liuxianchao] EthFw_initLinkArgs, macPort = 0, vlanCfg portCfi is 0, portPri is 0, portVID is 400 [MCU2_0] 30.953066 s: [LXC] phyCfg->phyAddr = 0, portNum = 2 [MCU2_0] 30.953106 s: [untouch:liuxianchao] EthFw_initLinkArgs, macPort = 2, vlanCfg portCfi is 0, portPri is 2, portVID is 402 [MCU2_0] 30.953490 s: EnetPhy_bindDriver: PHY 0: OUI:2b8094 Model:03 Ver:02 <-> 'generic' : OK [MCU2_0] 30.953582 s: [LXC] phyCfg->phyAddr = 0, portNum = 4 [MCU2_0] 30.953614 s: [untouch:liuxianchao] EthFw_initLinkArgs, macPort = 4, vlanCfg portCfi is 0, portPri is 4, portVID is 404 [MCU2_0] 30.953945 s: EnetPhy_bindDriver: PHY 0: OUI:2b8094 Model:03 Ver:02 <-> 'generic' : OK [MCU2_0] 30.954029 s: [LXC] phyCfg->phyAddr = 1, portNum = 5 [MCU2_0] 30.954060 s: [untouch:liuxianchao] EthFw_initLinkArgs, macPort = 5, vlanCfg portCfi is 0, portPri is 5, portVID is 405 [MCU2_0] 30.954433 s: EnetPhy_bindDriver: PHY 1: OUI:2b8094 Model:03 Ver:02 <-> 'generic' : OK [MCU2_0] 30.954498 s: PHY 0 is alive [MCU2_0] 30.954527 s: PHY 1 is alive [MCU2_0] 30.956292 s: ETHFW: Version : 0.01.01 [MCU2_0] 30.956347 s: ETHFW: Build Date: Sep 26, 2021 [MCU2_0] 30.956397 s: ETHFW: Build Time: 18:20:43 [MCU2_0] 30.956427 s: ETHFW: Commit SHA: a9710bfb [MCU2_0] 30.956456 s: ETHFW: Init ... DONE !!! [MCU2_0] 30.956480 s: ETHFW: Remove server Init ... !!! [MCU2_0] 30.957839 s: Remote demo device (core : mcu2_0) ..... [MCU2_0] 30.957904 s: ETHFW: Remove server Init ... DONE !!! [MCU2_0] 30.963890 s: Host MAC address: 70:ff:76:1d:92:c1 [MCU2_0] 31.007376 s: FVID2: Init ... !!! [MCU2_0] 31.007474 s: FVID2: Init ... Done !!! [MCU2_0] 31.007515 s: DSS: Init ... !!! [MCU2_0] 31.007536 s: DSS: Display type is eDP !!! [MCU2_0] 31.007557 s: DSS: SoC init ... !!! [MCU2_0] 31.007577 s: SCICLIENT: Sciclient_pmSetModuleState module=152 state=2 [MCU2_0] 31.007723 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.007752 s: SCICLIENT: Sciclient_pmSetModuleState module=297 state=2 [MCU2_0] 31.007890 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.007915 s: SCICLIENT: Sciclient_pmSetModuleState module=151 state=2 [MCU2_0] 31.008014 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.008040 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=9 parent=11 [MCU2_0] 31.008115 s: SCICLIENT: Sciclient_pmSetModuleClkParent success [MCU2_0] 31.008141 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=13 parent=18 [MCU2_0] 31.008207 s: SCICLIENT: Sciclient_pmSetModuleClkParent success [MCU2_0] 31.008232 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=1 parent=2 [MCU2_0] 31.008291 s: SCICLIENT: Sciclient_pmSetModuleClkParent success [MCU2_0] 31.008317 s: SCICLIENT: Sciclient_pmSetModuleClkFreq module=152 clk=1 freq=148500000 [MCU2_0] 31.009303 s: SCICLIENT: Sciclient_pmSetModuleClkFreq success [MCU2_0] 31.009339 s: SCICLIENT: Sciclient_pmModuleClkRequest module=152 clk=1 state=2 flag=0 [MCU2_0] 31.009460 s: SCICLIENT: Sciclient_pmModuleClkRequest success [MCU2_0] 31.009492 s: DSS: SoC init ... Done !!! [MCU2_0] 31.009513 s: DSS: Board init ... !!! [MCU2_0] 31.009532 s: DSS: Board init ... Done !!! [MCU2_0] 31.027920 s: DSS: Init ... Done !!! [MCU2_0] 31.027979 s: VHWA: VPAC Init ... !!! [MCU2_0] 31.028005 s: SCICLIENT: Sciclient_pmSetModuleState module=290 state=2 [MCU2_0] 31.028151 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.028179 s: VHWA: LDC Init ... !!! [MCU2_0] 31.031037 s: VHWA: LDC Init ... Done !!! [MCU2_0] 31.031087 s: VHWA: MSC Init ... !!! [MCU2_0] 31.039282 s: VHWA: MSC Init ... Done !!! [MCU2_0] 31.039330 s: VHWA: NF Init ... !!! [MCU2_0] 31.040792 s: VHWA: NF Init ... Done !!! [MCU2_0] 31.040841 s: VHWA: VISS Init ... !!! [MCU2_0] 31.046551 s: VHWA: VISS Init ... Done !!! [MCU2_0] 31.046602 s: VHWA: VPAC Init ... Done !!! [MCU2_0] 31.046639 s: VX_ZONE_INIT:Enabled [MCU2_0] 31.046661 s: VX_ZONE_ERROR:Enabled [MCU2_0] 31.046680 s: VX_ZONE_WARNING:Enabled [MCU2_0] 31.047726 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target IPU1-0 [MCU2_0] 31.048005 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_NF [MCU2_0] 31.048267 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_LDC1 [MCU2_0] 31.048570 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_MSC1 [MCU2_0] 31.048831 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_MSC2 [MCU2_0] 31.049121 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_VISS1 [MCU2_0] 31.049457 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE1 [MCU2_0] 31.049759 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE2 [MCU2_0] 31.050039 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DISPLAY1 [MCU2_0] 31.050324 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DISPLAY2 [MCU2_0] 31.050646 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CSITX [MCU2_0] 31.050930 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE3 [MCU2_0] 31.051221 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE4 [MCU2_0] 31.051560 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE5 [MCU2_0] 31.051867 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE6 [MCU2_0] 31.052147 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE7 [MCU2_0] 31.052489 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE8 [MCU2_0] 31.052539 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!! [MCU2_0] 31.052567 s: APP: OpenVX Target kernel init ... !!! [MCU2_0] 31.064277 s: APP: OpenVX Target kernel init ... Done !!! [MCU2_0] 31.064334 s: CSI2RX: Init ... !!! [MCU2_0] 31.064353 s: SCICLIENT: Sciclient_pmSetModuleState module=25 state=2 [MCU2_0] 31.064492 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.064525 s: SCICLIENT: Sciclient_pmSetModuleState module=26 state=2 [MCU2_0] 31.064620 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.064644 s: SCICLIENT: Sciclient_pmSetModuleState module=27 state=2 [MCU2_0] 31.064721 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.064747 s: SCICLIENT: Sciclient_pmSetModuleState module=147 state=2 [MCU2_0] 31.064802 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.064826 s: SCICLIENT: Sciclient_pmSetModuleState module=148 state=2 [MCU2_0] 31.065040 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.065756 s: CSI2RX: Init ... Done !!! [MCU2_0] 31.065807 s: CSI2TX: Init ... !!! [MCU2_0] 31.065830 s: SCICLIENT: Sciclient_pmSetModuleState module=25 state=2 [MCU2_0] 31.065898 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.065926 s: SCICLIENT: Sciclient_pmSetModuleState module=28 state=2 [MCU2_0] 31.066013 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.066038 s: SCICLIENT: Sciclient_pmSetModuleState module=296 state=2 [MCU2_0] 31.066111 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_0] 31.066623 s: CSI2TX: Init ... Done !!! [MCU2_0] 31.066669 s: ISS: Init ... !!! [MCU2_0] 31.066695 s: Found sensor IMX390-UB953_D3 at location 0 [MCU2_0] 31.066767 s: LXC 0001111: IssSensor_AR0233_Init, 174, status = 255 [MCU2_0] 31.066803 s: Found sensor AR0233-UB953_MARS at location 1 [MCU2_0] 31.066831 s: Found sensor AR0820-UB953_LI at location 2 [MCU2_0] 31.066857 s: Found sensor UB9xxx_RAW12_TESTPATTERN at location 3 [MCU2_0] 31.066887 s: Found sensor UB96x_UYVY_TESTPATTERN at location 4 [MCU2_0] 31.066915 s: Found sensor GW_AR0233_UYVY at location 5 [MCU2_0] 31.066941 s: IssSensor_Init ... Done !!! [MCU2_0] 31.067011 s: vissRemoteServer_Init ... Done !!! [MCU2_0] 31.067064 s: IttRemoteServer_Init ... Done !!! [MCU2_0] 31.067090 s: UDMA Copy: Init ... !!! [MCU2_0] 31.068553 s: UDMA Copy: Init ... Done !!! [MCU2_0] 31.068606 s: APP: Init ... Done !!! [MCU2_0] 31.068629 s: APP: Run ... !!! [MCU2_0] 31.068650 s: IPC: Starting echo test ... [MCU2_0] 31.071105 s: APP: Run ... Done !!! [MCU2_0] 31.071304 s: [MCU2_0] 31.071404 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 31.071454 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 31.071501 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 31.076308 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 31.076381 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 31.077948 s: [MCU2_0] CPSW NIMU application, IP address I/F 1: 192.168.10.33 [MCU2_0] 31.078726 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[.] C66X_1[P] C66X_2[.] C7X_1[.] [MCU2_0] 31.078906 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[.] C66X_1[P] C66X_2[P] C7X_1[.] [MCU2_0] 31.079026 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[.] [MCU2_0] 31.079121 s: IPC: Echo status: mpu1_0[x] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[P] [MCU2_0] 31.176978 s: [MCU2_0] 31.177043 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 31.177080 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 31.177122 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 31.181945 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 31.181996 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 31.281963 s: [MCU2_0] 31.282022 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 31.282060 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 31.282102 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 31.286927 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 31.286978 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 [MCU2_0] 31.401125 s: EthFw: TimeSync PTP enabled [MCU2_0] 33.406126 s: Function:CpswProxyServer_attachExtHandlerCb,HostId:0,CpswType:6 [MCU2_0] 34.775420 s: Function:CpswProxyServer_registerMacHandlerCb,HostId:0,Handle:a32049fc,CoreKey:38acb7e6, MacAddress:70:ff:76:1d:92:c2, FlowIdx:172, FlowIdxOffset:0 [MCU2_0] 34.778503 s: Cpsw_ioctlInternal: CPSW: Registered MAC address.ALE entry:13, Policer Entry:2 [MCU2_0] 36.454411 s: [MCU2_0] 36.454481 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 36.454523 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 36.454567 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 36.459372 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 36.459427 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 36.559974 s: [MCU2_0] 36.560035 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 36.560074 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 36.560137 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 36.564942 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 36.564995 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 36.664960 s: [MCU2_0] 36.665017 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 36.665053 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 36.665096 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 36.669932 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 36.669982 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 [MCU2_0] 41.854407 s: [MCU2_0] 41.854478 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 41.854519 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 41.854563 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 41.859391 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 41.859446 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 41.959941 s: [MCU2_0] 41.960005 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 41.960044 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 41.960086 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 41.964908 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 41.964960 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 42.064983 s: [MCU2_0] 42.065039 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 42.065079 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 42.065122 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 42.069955 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 42.070006 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 [MCU2_0] 47.254405 s: [MCU2_0] 47.254477 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 47.254520 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 47.254564 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 47.259411 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 47.259462 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 47.359961 s: [MCU2_0] 47.360022 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 47.360063 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 47.360106 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 47.364930 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 47.364983 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 47.464951 s: [MCU2_0] 47.465013 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 47.465052 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 47.465096 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 47.469918 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 47.469971 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 [MCU2_0] 52.654409 s: [MCU2_0] 52.654479 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 52.654522 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 52.654564 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 52.659384 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 52.659439 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 52.759984 s: [MCU2_0] 52.760047 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 52.760086 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 52.760153 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 52.764954 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 52.765005 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 52.864970 s: [MCU2_0] 52.865024 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 52.865062 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 52.865103 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 52.869940 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 52.869990 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 [MCU2_0] 58.054404 s: [MCU2_0] 58.054472 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 58.054511 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 58.054552 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 58.059401 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 58.059457 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 58.159947 s: [MCU2_0] 58.160008 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 58.160047 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 58.160090 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 58.164918 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 58.164967 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 58.264933 s: [MCU2_0] 58.264989 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 58.265026 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 58.265071 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 58.269903 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 58.269952 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 [MCU2_0] 63.454412 s: [MCU2_0] 63.454484 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 63.454525 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 63.454570 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 63.459373 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 63.459430 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 63.559971 s: [MCU2_0] 63.560031 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_1] 3.547293 s: CIO: Init ... Done !!! [MCU2_1] 3.547358 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz> [MCU2_1] 3.547399 s: APP: Init ... !!! [MCU2_1] 3.547419 s: SCICLIENT: Init ... !!! [MCU2_1] 3.547605 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla] [MCU2_1] 3.547639 s: SCICLIENT: DMSC FW revision 0x15 [MCU2_1] 3.547662 s: SCICLIENT: DMSC FW ABI revision 3.1 [MCU2_1] 3.547686 s: SCICLIENT: Init ... Done !!! [MCU2_1] 3.547707 s: UDMA: Init ... !!! [MCU2_1] 3.548806 s: UDMA: Init ... Done !!! [MCU2_1] 3.548853 s: MEM: Init ... !!! [MCU2_1] 3.548889 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e2000000 of size 16777216 bytes !!! [MCU2_1] 3.548941 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 3620000 of size 131072 bytes !!! [MCU2_1] 3.548991 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000000) @ d9000000 of size 117440512 bytes !!! [MCU2_1] 3.549037 s: MEM: Init ... Done !!! [MCU2_1] 3.549058 s: IPC: Init ... !!! [MCU2_1] 3.549086 s: IPC: 6 CPUs participating in IPC !!! [MCU2_1] 3.549123 s: IPC: Waiting for HLOS to be ready ... !!! [MCU2_1] 30.912499 s: IPC: HLOS is ready !!! [MCU2_1] 30.917801 s: IPC: Init ... Done !!! [MCU2_1] 30.917855 s: APP: Syncing with 5 CPUs ... !!! [MCU2_1] 30.917892 s: APP: Syncing with 5 CPUs ... Done !!! [MCU2_1] 30.917920 s: REMOTE_SERVICE: Init ... !!! [MCU2_1] 30.919735 s: REMOTE_SERVICE: Init ... Done !!! [MCU2_1] 30.919796 s: FVID2: Init ... !!! [MCU2_1] 30.919855 s: FVID2: Init ... Done !!! [MCU2_1] 30.919884 s: VHWA: DMPAC: Init ... !!! [MCU2_1] 30.919904 s: SCICLIENT: Sciclient_pmSetModuleState module=48 state=2 [MCU2_1] 30.920042 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_1] 30.920073 s: SCICLIENT: Sciclient_pmSetModuleState module=305 state=2 [MCU2_1] 30.920518 s: SCICLIENT: Sciclient_pmSetModuleState success [MCU2_1] 30.920552 s: VHWA: DOF Init ... !!! [MCU2_1] 30.927878 s: VHWA: DOF Init ... Done !!! [MCU2_1] 30.927928 s: VHWA: SDE Init ... !!! [MCU2_1] 30.929997 s: VHWA: SDE Init ... Done !!! [MCU2_1] 30.930041 s: VHWA: DMPAC: Init ... Done !!! [MCU2_1] 30.930066 s: VHWA: Codec: Init ... !!! [MCU2_1] 30.930086 s: VHWA: VDEC Init ... !!! [MCU2_1] 30.943672 s: VHWA: VDEC Init ... Done !!! [MCU2_1] 30.943725 s: VHWA: VENC Init ... !!! [MCU2_1] 30.943868 s: MM_ENC_Init: No OCM RAM pool available, fallback to DDR mode for above mp params [MCU2_1] 30.985244 s: VHWA: VENC Init ... Done !!! [MCU2_1] 30.985293 s: VHWA: Init ... Done !!! [MCU2_1] 30.985329 s: VX_ZONE_INIT:Enabled [MCU2_1] 30.985352 s: VX_ZONE_ERROR:Enabled [MCU2_1] 30.985409 s: VX_ZONE_WARNING:Enabled [MCU2_1] 30.986343 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DMPAC_SDE [MCU2_1] 30.986597 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DMPAC_DOF [MCU2_1] 30.986810 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VDEC1 [MCU2_1] 30.987020 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VDEC2 [MCU2_1] 30.987226 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VENC1 [MCU2_1] 30.987474 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VENC2 [MCU2_1] 30.987527 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!! [MCU2_1] 30.987556 s: APP: OpenVX Target kernel init ... !!! [MCU2_1] 30.987901 s: APP: OpenVX Target kernel init ... Done !!! [MCU2_1] 30.987943 s: UDMA Copy: Init ... !!! [MCU2_1] 30.989398 s: UDMA Copy: Init ... Done !!! [MCU2_1] 30.989452 s: APP: Init ... Done !!! [MCU2_1] 30.989477 s: APP: Run ... !!! [MCU2_1] 30.989497 s: IPC: Starting echo test ... [MCU2_1] 30.991617 s: APP: Run ... Done !!! [MCU2_1] 30.992721 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[.] C7X_1[.] [MCU2_1] 30.992805 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[.] [MCU2_1] 30.992868 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[P] [MCU2_1] 31.078410 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[P] [C6x_1 ] 3.655613 s: CIO: Init ... Done !!! [C6x_1 ] 3.655645 s: ### CPU Frequency <ORG = 1350000000 Hz>, <NEW = 1350000000 Hz> [C6x_1 ] 3.655658 s: APP: Init ... !!! [C6x_1 ] 3.655665 s: SCICLIENT: Init ... !!! [C6x_1 ] 3.655846 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla] [C6x_1 ] 3.655857 s: SCICLIENT: DMSC FW revision 0x15 [C6x_1 ] 3.655865 s: SCICLIENT: DMSC FW ABI revision 3.1 [C6x_1 ] 3.655875 s: SCICLIENT: Init ... Done !!! [C6x_1 ] 3.655883 s: UDMA: Init ... !!! [C6x_1 ] 3.657038 s: UDMA: Init ... Done !!! [C6x_1 ] 3.657061 s: MEM: Init ... !!! [C6x_1 ] 3.657072 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e4000000 of size 16777216 bytes !!! [C6x_1 ] 3.657088 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!! [C6x_1 ] 3.657103 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ e5000000 of size 50331648 bytes !!! [C6x_1 ] 3.657118 s: MEM: Init ... Done !!! [C6x_1 ] 3.657126 s: IPC: Init ... !!! [C6x_1 ] 3.657138 s: IPC: 6 CPUs participating in IPC !!! [C6x_1 ] 3.657151 s: IPC: Waiting for HLOS to be ready ... !!! [C6x_1 ] 29.818252 s: IPC: HLOS is ready !!! [C6x_1 ] 29.821978 s: IPC: Init ... Done !!! [C6x_1 ] 29.822013 s: APP: Syncing with 5 CPUs ... !!! [C6x_1 ] 30.917892 s: APP: Syncing with 5 CPUs ... Done !!! [C6x_1 ] 30.917906 s: REMOTE_SERVICE: Init ... !!! [C6x_1 ] 30.918678 s: REMOTE_SERVICE: Init ... Done !!! [C6x_1 ] 30.918720 s: VX_ZONE_INIT:Enabled [C6x_1 ] 30.918733 s: VX_ZONE_ERROR:Enabled [C6x_1 ] 30.918743 s: VX_ZONE_WARNING:Enabled [C6x_1 ] 30.919649 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!! [C6x_1 ] 30.919670 s: APP: OpenVX Target kernel init ... !!! [C6x_1 ] 30.919953 s: APP: OpenVX Target kernel init ... Done !!! [C6x_1 ] 30.919971 s: UDMA Copy: Init ... !!! [C6x_1 ] 30.923216 s: UDMA Copy: Init ... Done !!! [C6x_1 ] 30.923234 s: APP: Init ... Done !!! [C6x_1 ] 30.923928 s: APP: Run ... !!! [C6x_1 ] 30.923938 s: IPC: Starting echo test ... [C6x_1 ] 30.925027 s: APP: Run ... Done !!! [C6x_1 ] 30.925348 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[s] C66X_2[x] C7X_1[P] [C6x_1 ] 30.925759 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[s] C66X_2[P] C7X_1[P] [C6x_1 ] 30.992519 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] C66X_1[s] C66X_2[P] C7X_1[P] [C6x_1 ] 31.078269 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] C66X_1[s] C66X_2[P] C7X_1[P] [C6x_2 ] 3.740178 s: CIO: Init ... Done !!! [C6x_2 ] 3.740211 s: ### CPU Frequency <ORG = 1350000000 Hz>, <NEW = 1350000000 Hz> [C6x_2 ] 3.740224 s: APP: Init ... !!! [C6x_2 ] 3.740232 s: SCICLIENT: Init ... !!! [C6x_2 ] 3.740413 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla] [C6x_2 ] 3.740425 s: SCICLIENT: DMSC FW revision 0x15 [C6x_2 ] 3.740434 s: SCICLIENT: DMSC FW ABI revision 3.1 [C6x_2 ] 3.740443 s: SCICLIENT: Init ... Done !!! [C6x_2 ] 3.740452 s: UDMA: Init ... !!! [C6x_2 ] 3.741614 s: UDMA: Init ... Done !!! [C6x_2 ] 3.741637 s: MEM: Init ... !!! [C6x_2 ] 3.741648 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e8000000 of size 16777216 bytes !!! [C6x_2 ] 3.741665 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!! [C6x_2 ] 3.741680 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ e9000000 of size 50331648 bytes !!! [C6x_2 ] 3.741696 s: MEM: Init ... Done !!! [C6x_2 ] 3.741704 s: IPC: Init ... !!! [C6x_2 ] 3.741717 s: IPC: 6 CPUs participating in IPC !!! [C6x_2 ] 3.741730 s: IPC: Waiting for HLOS to be ready ... !!! [C6x_2 ] 29.967487 s: IPC: HLOS is ready !!! [C6x_2 ] 29.971044 s: IPC: Init ... Done !!! [C6x_2 ] 29.971074 s: APP: Syncing with 5 CPUs ... !!! [C6x_2 ] 30.917892 s: APP: Syncing with 5 CPUs ... Done !!! [C6x_2 ] 30.917906 s: REMOTE_SERVICE: Init ... !!! [C6x_2 ] 30.918688 s: REMOTE_SERVICE: Init ... Done !!! [C6x_2 ] 30.918726 s: VX_ZONE_INIT:Enabled [C6x_2 ] 30.918743 s: VX_ZONE_ERROR:Enabled [C6x_2 ] 30.918752 s: VX_ZONE_WARNING:Enabled [C6x_2 ] 30.919644 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!! [C6x_2 ] 30.919664 s: APP: OpenVX Target kernel init ... !!! [C6x_2 ] 30.919958 s: APP: OpenVX Target kernel init ... Done !!! [C6x_2 ] 30.919978 s: UDMA Copy: Init ... !!! [C6x_2 ] 30.923495 s: UDMA Copy: Init ... Done !!! [C6x_2 ] 30.923513 s: APP: Init ... Done !!! [C6x_2 ] 30.924209 s: APP: Run ... !!! [C6x_2 ] 30.924231 s: IPC: Starting echo test ... [C6x_2 ] 30.925416 s: APP: Run ... Done !!! [C6x_2 ] 30.925764 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[s] C7X_1[.] [C6x_2 ] 30.925804 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[s] C7X_1[P] [C6x_2 ] 30.992545 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] C66X_1[P] C66X_2[s] C7X_1[P] [C6x_2 ] 31.078305 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] C66X_1[P] C66X_2[s] C7X_1[P] [C7x_1 ] 3.939633 s: CIO: Init ... Done !!! [C7x_1 ] 3.939655 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz> [C7x_1 ] 3.939671 s: APP: Init ... !!! [C7x_1 ] 3.939678 s: SCICLIENT: Init ... !!! [C7x_1 ] 3.939847 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla] [C7x_1 ] 3.939861 s: SCICLIENT: DMSC FW revision 0x15 [C7x_1 ] 3.939871 s: SCICLIENT: DMSC FW ABI revision 3.1 [C7x_1 ] 3.939881 s: SCICLIENT: Init ... Done !!! [C7x_1 ] 3.939889 s: UDMA: Init ... !!! [C7x_1 ] 3.940731 s: UDMA: Init ... Done !!! [C7x_1 ] 3.940743 s: MEM: Init ... !!! [C7x_1 ] 3.940753 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ 100000000 of size 1073741824 bytes !!! [C7x_1 ] 3.940773 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 70020000 of size 8159232 bytes !!! [C7x_1 ] 3.940791 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 64800000 of size 491520 bytes !!! [C7x_1 ] 3.940808 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 64e00000 of size 16384 bytes !!! [C7x_1 ] 3.940825 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ ec000000 of size 268435456 bytes !!! [C7x_1 ] 3.940843 s: MEM: Init ... Done !!! [C7x_1 ] 3.940850 s: IPC: Init ... !!! [C7x_1 ] 3.940860 s: IPC: 6 CPUs participating in IPC !!! [C7x_1 ] 3.940872 s: IPC: Waiting for HLOS to be ready ... !!! [C7x_1 ] 30.375878 s: IPC: HLOS is ready !!! [C7x_1 ] 30.377895 s: IPC: Init ... Done !!! [C7x_1 ] 30.377909 s: APP: Syncing with 5 CPUs ... !!! [C7x_1 ] 30.917893 s: APP: Syncing with 5 CPUs ... Done !!! [C7x_1 ] 30.917910 s: REMOTE_SERVICE: Init ... !!! [C7x_1 ] 30.918233 s: REMOTE_SERVICE: Init ... Done !!! [C7x_1 ] 30.918255 s: VX_ZONE_INIT:Enabled [C7x_1 ] 30.918265 s: VX_ZONE_ERROR:Enabled [C7x_1 ] 30.918275 s: VX_ZONE_WARNING:Enabled [C7x_1 ] 30.918520 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!! [C7x_1 ] 30.918534 s: APP: OpenVX Target kernel init ... !!! [C7x_1 ] 30.918617 s: APP: OpenVX Target kernel init ... Done !!! [C7x_1 ] 30.918631 s: APP: Init ... Done !!! [C7x_1 ] 30.918640 s: APP: Run ... !!! [C7x_1 ] 30.918648 s: IPC: Starting echo test ... [C7x_1 ] 30.919117 s: APP: Run ... Done !!! [C7x_1 ] 30.925359 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[x] C7X_1[s] [C7x_1 ] 30.925756 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[P] C7X_1[s] [C7x_1 ] 30.992565 s: IPC: Echo status: mpu1_0[x] mcu2_0[x] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[s] [C7x_1 ] 31.078327 s: IPC: Echo status: mpu1_0[x] mcu2_0[P] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[s] [MCU2_0] 95.854409 s: [MCU2_0] 95.854481 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 95.854519 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 95.854563 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 95.859387 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 95.859445 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 95.959932 s: [MCU2_0] 95.959995 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 95.960034 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 95.960076 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 95.964904 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 95.964960 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 96.064978 s: [MCU2_0] 96.065034 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 96.065074 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 96.065115 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 96.069949 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 96.069998 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 root@j7-evm:/opt/vision_apps# root@j7-evm:/opt/vision_apps# [MCU2_0] 101.254408 s: [MCU2_0] 101.254477 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 101.254517 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 101.254561 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 101.259405 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 101.259457 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 101.359954 s: [MCU2_0] 101.360012 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 101.360051 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 101.360096 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 101.364925 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 101.364981 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 101.464944 s: [MCU2_0] 101.465013 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 101.465055 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 101.465099 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 101.469912 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 101.469965 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 root@j7-evm:/opt/vision_apps# root@j7-evm:/opt/vision_apps# [MCU2_0] 106.654407 s: [MCU2_0] 106.654477 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 106.654518 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 106.654560 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 106.659381 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 106.659435 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 106.759976 s: [MCU2_0] 106.760042 s: [LXC]: GenericPhy_reset. PHY 0: reset [MCU2_0] 106.760081 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 106.760146 s: [LXC]: Bcm89881_config hPhy->addr = 0 [MCU2_0] 106.764947 s: [LXC]: hunmaster1111 finished. hPhy->addr = 0 [MCU2_0] 106.765004 s: [LXC]: hunmaster2222 finished. hPhy->addr = 0 [MCU2_0] 106.864964 s: [MCU2_0] 106.865022 s: [LXC]: GenericPhy_reset. PHY 1: reset [MCU2_0] 106.865061 s: Bcm89881_config start, master:1, speed:100, loopback:0 [MCU2_0] 106.865102 s: [LXC]: Bcm89881_config hPhy->addr = 1 [MCU2_0] 106.869932 s: [LXC]: hunmaster1111 finished. hPhy->addr = 1 [MCU2_0] 106.869983 s: [LXC]: hunmaster2222 finished. hPhy->addr = 1 root@j7-evm:/opt/vision_apps# ^C root@j7-evm:/opt/vision_apps# CTRL-A Z for help | 115200 8N1 | NOR | Minicom 2.7.1 | VT102 | Offline | ttyUSB0

The pdk_patch 1:

commit 04193e5764b58195255051114a2d2ea6007f89b0

Author: liuxianchao <liuxianchao@untouch-tech.com>

Date: Fri Sep 24 10:39:26 2021 +0800

push test code for cpsw9g rgmii5

diff --git a/packages/ti/board/src/devices/common/common.c b/packages/ti/board/src/devices/common/common.c

index 600aeed..4e2ae7c 100755

--- a/packages/ti/board/src/devices/common/common.c

+++ b/packages/ti/board/src/devices/common/common.c

@@ -40,6 +40,17 @@

#include "common.h"

+#include <ti/csl/soc.h>

+#include <ti/csl/csl_types.h>

+#include <ti/drv/gpio/GPIO.h>

+#include <ti/drv/gpio/soc/GPIO_soc.h>

+#include <ti/drv/gpio/test/led_blink/src/GPIO_board.h>

+

+/*

+ TODO:

+ PHY3_RST_N: low --> high

+*/

+

/**

* \brief Delay generation function

*

diff --git a/packages/ti/board/src/devices/fpd/ds90ub960.c b/packages/ti/board/src/devices/fpd/ds90ub960.c

index da1a5ea..ad856eb 100755

--- a/packages/ti/board/src/devices/fpd/ds90ub960.c

+++ b/packages/ti/board/src/devices/fpd/ds90ub960.c

@@ -674,6 +674,7 @@ Board_STATUS Board_fpdUb960ReadReg(void *handle,

return ret;

}

+#define UNTOUCH

/**

* \brief Get ub960 i2c address.

*

@@ -694,8 +695,13 @@ void Board_fpdU960GetI2CAddr(uint8_t *chNum,

//J7_TODO: Need to update to make it generic across the devices and platforms

if (csiInst == BOARD_CSI_INST_0)

{

+#ifdef UNTOUCH

+ *chNum = 3U;

+ *i2cAddr = 0x3AU;

+#else

*chNum = 6U;

*i2cAddr = 0x3DU;

+#endif

}

else if (csiInst == BOARD_CSI_INST_1)

{

diff --git a/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c b/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c

index 4745d2b..64c6b82 100755

--- a/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c

+++ b/packages/ti/board/src/j721e_evm/J721E_pinmux_data_gesi_cpsw9g.c

@@ -23,10 +23,10 @@

static pinmuxPerCfg_t gCpsw9g0PinCfg[] =

{

/* MyCPSW9G3 -> CLKOUT -> AA25 */

- {

- PIN_PRG0_PRU1_GPO10, PIN_MODE(0) | \

- ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

- },

+ // {

+ // PIN_PRG0_PRU1_GPO10, PIN_MODE(0) | \

+ // ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+ // },

{PINMUX_END}

};

@@ -36,14 +36,16 @@ static pinmuxModuleCfg_t gCpsw9gPinCfg[] =

{PINMUX_END}

};

-

+/*

+ TODO: 配置PHY复位引脚,I2C扩展芯片P20

+*/

static pinmuxPerCfg_t gGpio0PinCfg[] =

{

/* MyGPIO0 -> GPIO0_96 -> T23 */

- {

- PIN_RGMII5_RD0, PIN_MODE(7) | \

- ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

- },

+ // {

+ // PIN_RGMII5_RD0, PIN_MODE(7) | \

+ // ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ // },

/* MyGPIO0 -> GPIO0_104 -> W26 */

{

PIN_RGMII6_RXC, PIN_MODE(7) | \

@@ -74,6 +76,21 @@ static pinmuxPerCfg_t gMdio0PinCfg[] =

{PINMUX_END}

};

+// static pinmuxPerCfg_t gMdio0PinCfg[] =

+// {

+// /* MyMDIO1 -> PIN_PRG1_MDIO0_MDC -> AD18 */

+// {

+// PIN_PRG1_MDIO0_MDC, PIN_MODE(0) | \

+// ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+// },

+// /* MyMDIO1 -> PIN_PRG1_MDIO0_MDIO -> AD19 */

+// {

+// PIN_PRG1_MDIO0_MDIO, PIN_MODE(0) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// {PINMUX_END}

+// };

+

static pinmuxModuleCfg_t gMdioPinCfg[] =

{

{0, TRUE, gMdio0PinCfg},

@@ -276,67 +293,132 @@ static pinmuxPerCfg_t gRgmii1PinCfg[] =

{PINMUX_END}

};

-static pinmuxPerCfg_t gRgmii2PinCfg[] =

+// static pinmuxPerCfg_t gRgmii2PinCfg[] =

+// {

+// /* MyRGMII2 -> RGMII2_RD0 -> AE22 */

+// {

+// PIN_PRG1_PRU1_GPO0, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyRGMII2 -> RGMII2_RD1 -> AG23 */

+// {

+// PIN_PRG1_PRU1_GPO1, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyRGMII2 -> RGMII2_RD2 -> AF23 */

+// {

+// PIN_PRG1_PRU1_GPO2, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyRGMII2 -> RGMII2_RD3 -> AD23 */

+// {

+// PIN_PRG1_PRU1_GPO3, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyRGMII2 -> RGMII2_RXC -> AE23 */

+// {

+// PIN_PRG1_PRU1_GPO6, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyRGMII2 -> RGMII2_RX_CTL -> AH24 */

+// {

+// PIN_PRG1_PRU1_GPO4, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyRGMII2 -> RGMII2_TD0 -> AJ25 */

+// {

+// PIN_PRG1_PRU1_GPO11, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+// },

+// /* MyRGMII2 -> RGMII2_TD1 -> AH25 */

+// {

+// PIN_PRG1_PRU1_GPO12, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+// },

+// /* MyRGMII2 -> RGMII2_TD2 -> AG25 */

+// {

+// PIN_PRG1_PRU1_GPO13, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+// },

+// /* MyRGMII2 -> RGMII2_TD3 -> AH26 */

+// {

+// PIN_PRG1_PRU1_GPO14, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

+// },

+// /* MyRGMII2 -> RGMII2_TXC -> AJ26 */

+// {

+// PIN_PRG1_PRU1_GPO16, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// /* MyRGMII2 -> RGMII2_TX_CTL -> AJ27 */

+// {

+// PIN_PRG1_PRU1_GPO15, PIN_MODE(4) | \

+// ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+// },

+// {PINMUX_END}

+// };

+

+static pinmuxPerCfg_t gRgmii5PinCfg[] =

{

- /* MyRGMII2 -> RGMII2_RD0 -> AE22 */

+ /* MyRGMII5 -> RGMII5_RD0 */

{

- PIN_PRG1_PRU1_GPO0, PIN_MODE(4) | \

+ PIN_RGMII5_RD0, PIN_MODE(0) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyRGMII2 -> RGMII2_RD1 -> AG23 */

+ /* MyRGMII5 -> RGMII5_RD1 */

{

- PIN_PRG1_PRU1_GPO1, PIN_MODE(4) | \

+ PIN_RGMII5_RD1, PIN_MODE(0) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyRGMII2 -> RGMII2_RD2 -> AF23 */

+ /* MyRGMII5 -> RGMII5_RD2 */

{

- PIN_PRG1_PRU1_GPO2, PIN_MODE(4) | \

+ PIN_RGMII5_RD2, PIN_MODE(0) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyRGMII2 -> RGMII2_RD3 -> AD23 */

+ /* MyRGMII5 -> RGMII5_RD3 */

{

- PIN_PRG1_PRU1_GPO3, PIN_MODE(4) | \

+ PIN_RGMII5_RD3, PIN_MODE(0) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyRGMII2 -> RGMII2_RXC -> AE23 */

+ /* MyRGMII5 -> RGMII5_RXC */

{

- PIN_PRG1_PRU1_GPO6, PIN_MODE(4) | \

+ PIN_RGMII5_RXC, PIN_MODE(0) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyRGMII2 -> RGMII2_RX_CTL -> AH24 */

+ /* MyRGMII5 -> RGMII5_RX_CTL */

{

- PIN_PRG1_PRU1_GPO4, PIN_MODE(4) | \

+ PIN_RGMII5_RX_CTL, PIN_MODE(0) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

- /* MyRGMII2 -> RGMII2_TD0 -> AJ25 */

+ /* MyRGMII5 -> RGMII5_TD0 */

{

- PIN_PRG1_PRU1_GPO11, PIN_MODE(4) | \

+ PIN_RGMII5_TD0, PIN_MODE(0) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

- /* MyRGMII2 -> RGMII2_TD1 -> AH25 */

+ /* MyRGMII5 -> RGMII5_TD1 */

{

- PIN_PRG1_PRU1_GPO12, PIN_MODE(4) | \

+ PIN_RGMII5_TD1, PIN_MODE(0) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

- /* MyRGMII2 -> RGMII2_TD2 -> AG25 */

+ /* MyRGMII5 -> RGMII5_TD2 */

{

- PIN_PRG1_PRU1_GPO13, PIN_MODE(4) | \

+ PIN_RGMII5_TD2, PIN_MODE(0) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

- /* MyRGMII2 -> RGMII2_TD3 -> AH26 */

+ /* MyRGMII5 -> RGMII5_TD3 */

{

- PIN_PRG1_PRU1_GPO14, PIN_MODE(4) | \

+ PIN_RGMII5_TD3, PIN_MODE(0) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

- /* MyRGMII2 -> RGMII2_TXC -> AJ26 */

+ /* MyRGMII5 -> RGMII5_TXC */

{

- PIN_PRG1_PRU1_GPO16, PIN_MODE(4) | \

- ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ PIN_RGMII5_TXC, PIN_MODE(0) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

- /* MyRGMII2 -> RGMII2_TX_CTL -> AJ27 */

+ /* MyRGMII5 -> RGMII5_TX_CTL */

{

- PIN_PRG1_PRU1_GPO15, PIN_MODE(4) | \

- ((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

+ PIN_RGMII5_TX_CTL, PIN_MODE(0) | \

+ ((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

{PINMUX_END}

};

@@ -476,7 +558,8 @@ static pinmuxModuleCfg_t gRgmiiPinCfg[] =

{3, TRUE, gRgmii3PinCfg},

{4, TRUE, gRgmii4PinCfg},

{1, TRUE, gRgmii1PinCfg},

- {2, TRUE, gRgmii2PinCfg},

+ {5, TRUE, gRgmii5PinCfg},

+ // {2, TRUE, gRgmii2PinCfg},

{PINMUX_END}

};

diff --git a/packages/ti/board/src/j721e_evm/board_ethernet_config.c b/packages/ti/board/src/j721e_evm/board_ethernet_config.c

index 575b2e2..35584b6 100755

--- a/packages/ti/board/src/j721e_evm/board_ethernet_config.c

+++ b/packages/ti/board/src/j721e_evm/board_ethernet_config.c

@@ -704,28 +704,32 @@ Board_STATUS Board_ethConfigCpsw9g(void)

uint8_t portNum;

/* On J721E EVM to use all 8 ports simultaneously, we use below configuration

- RGMII Ports - 1,3,4,8. QSGMII ports - 2 (main),5,6,7 (sub)*/

+ //RGMII Ports - 1,3,4,8. QSGMII ports - 2 (main),5,6,7 (sub)

+ RGMII Ports - 1,3,4,5. QSGMII ports - 2 (main),6,7,8 (sub)*/

+

/* Configures the CPSW9G RGMII ports */

for(portNum=0; portNum < BOARD_CPSW9G_PORT_MAX; portNum++)

{

- if ( 0U == portNum ||

- 2U == portNum ||

+ // if ( 0U == portNum ||

+ if ( 2U == portNum ||

3U == portNum ||

- 7U == portNum )

+ 4U == portNum )

{

status = Board_cpsw9gEthConfig(portNum, RGMII);

+ // status = Board_cpsw9gEthConfig(portNum, RMII);

}

else

{

- if (1U == portNum)

- {

- status = Board_cpsw9gEthConfig(portNum, QSGMII);

- }

- else

- {

- status = Board_cpsw9gEthConfig(portNum, QSGMII_SUB);

- }

+ status = Board_cpsw9gEthConfig(portNum, SGMII);

+ // if (1U == portNum)

+ // {

+ // status = Board_cpsw9gEthConfig(portNum, QSGMII);

+ // }

+ // else

+ // {

+ // status = Board_cpsw9gEthConfig(portNum, QSGMII_SUB);

+ // }

}

if(status != BOARD_SOK)

diff --git a/packages/ti/drv/enet/enet_component.mk b/packages/ti/drv/enet/enet_component.mk

index 82a75e7..2e51a04 100644

--- a/packages/ti/drv/enet/enet_component.mk

+++ b/packages/ti/drv/enet/enet_component.mk

@@ -302,12 +302,12 @@ endif

# 4 - Debug

# 5 - Verbose

ifeq ($(BUILD_PROFILE),debug)

- ENET_CFLAGS += -DENET_CFG_TRACE_LEVEL=4

+ ENET_CFLAGS += -DENET_CFG_TRACE_LEVEL=5

ENET_CFLAGS += -DENET_CFG_DEV_ERROR=1

ENET_CFLAGS += -DENETDMA_INSTRUMENTATION_ENABLED

ENET_CFLAGS += -DENETCPTS_INSTRUMENTATION_ENABLED

else

- ENET_CFLAGS += -DENET_CFG_TRACE_LEVEL=3

+ ENET_CFLAGS += -DENET_CFG_TRACE_LEVEL=5

endif

ifeq ($(SOC),$(filter $(SOC), am65xx))

diff --git a/packages/ti/drv/enet/examples/utils/V1/enet_appboardutils_j721e_evm.c b/packages/ti/drv/enet/examples/utils/V1/enet_appboardutils_j721e_evm.c

index 387b467..b461f63 100644

--- a/packages/ti/drv/enet/examples/utils/V1/enet_appboardutils_j721e_evm.c

+++ b/packages/ti/drv/enet/examples/utils/V1/enet_appboardutils_j721e_evm.c

@@ -266,11 +266,13 @@ void EnetBoard_initEthFw(void)

EnetBoard_configTorrentClks();

#endif

- if (Board_detectBoard(BOARD_ID_ENET))

- {

- status = Board_serdesCfgQsgmii();

- EnetAppUtils_assert(status == BOARD_SOK);

- }

+ // if (Board_detectBoard(BOARD_ID_ENET))

+ // {

+ // status = Board_serdesCfgQsgmii();

+ // EnetAppUtils_assert(status == BOARD_SOK);

+ // }

+ status = Board_serdesCfgSgmii();

+ EnetAppUtils_assert(status == BOARD_SOK);

#endif

}

@@ -351,8 +353,10 @@ uint32_t EnetBoard_getPhyAddr(Enet_Type enetType,

break;

case ENET_MAC_PORT_5:

- /* QSGMII port */

- phyAddr = 17U;

+ // /* QSGMII port */

+ // phyAddr = 17U;

+ /* RGMII port */

+ phyAddr = 0U;

break;

case ENET_MAC_PORT_6:

@@ -534,8 +538,10 @@ void EnetBoard_setPhyConfigRgmii(Enet_Type enetType,

(portNum == ENET_MAC_PORT_2) ||

(portNum == ENET_MAC_PORT_3) ||

(portNum == ENET_MAC_PORT_4) ||

+ (portNum == ENET_MAC_PORT_5) ||

(portNum == ENET_MAC_PORT_7) ||

(portNum == ENET_MAC_PORT_8));

+ EnetBoard_setEnetControl(enetType, 0U/* instId */, portNum, RGMII);

#elif defined (SOC_J7200)

if (enetType == ENET_CPSW_2G)

{

@@ -555,6 +561,7 @@ void EnetBoard_setPhyConfigRgmii(Enet_Type enetType,

phyCfg->phyAddr = 0U;

#else

phyCfg->phyAddr = EnetBoard_getPhyAddr(enetType, portNum);

+ printf("[LXC] phyCfg->phyAddr = %d, portNum = %d\n", phyCfg->phyAddr, portNum);

#endif

/* DP83867 specific configuration */

@@ -626,6 +633,7 @@ void EnetBoard_setPhyConfig(Enet_Type enetType,

if ( ENET_MAC_PORT_1 == portNum ||

ENET_MAC_PORT_3 == portNum ||

ENET_MAC_PORT_4 == portNum ||

+ ENET_MAC_PORT_5 == portNum ||

ENET_MAC_PORT_8 == portNum )

{

EnetBoard_setPhyConfigRgmii(enetType,

diff --git a/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux.c b/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux.c

index 0070c2b..726c756 100644

--- a/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux.c

+++ b/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux.c

@@ -86,7 +86,8 @@ int32_t EnetBoard_configEthFwPinmux (void)

/* Overwrite the ICSSG RGMII muc configurations with CPSW */

/* Below is CPSW9G QSGMII pinmux configuration,

RGMII Ports - 1,3,4,8. QSGMII ports - 2,5,6,7 */

- Board_pinmuxUpdate(gJ721E_MainPinmuxDataGesiCpsw9gQsgmii,

+ // Board_pinmuxUpdate(gJ721E_MainPinmuxDataGesiCpsw9gQsgmii,

+ Board_pinmuxUpdate(gJ721E_MainPinmuxDataGesiCpsw9g,

BOARD_SOC_DOMAIN_MAIN);

#elif defined(BUILD_MCU2_0) && defined(SOC_J7200)

/* Below is CPSW5G QSGMII pinmux configuration,

diff --git a/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux_j721e_data.c b/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux_j721e_data.c

index f4d2f90..0497db6 100644

--- a/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux_j721e_data.c

+++ b/packages/ti/drv/enet/examples/utils/V1/enet_board_pinmux_j721e_data.c

@@ -209,6 +209,8 @@ static pinmuxPerCfg_t gGpio2PinCfg_phyReset[] =

PIN_RGMII5_RD0, PIN_MODE(7) | \

((PIN_PULL_DISABLE | PIN_INPUT_ENABLE) & (~PIN_PULL_DIRECTION))

},

+

+ /* TODO: 配置复位引脚 */

{PINMUX_END}

};

diff --git a/packages/ti/drv/enet/examples/utils/enet_board_j7xevm.c b/packages/ti/drv/enet/examples/utils/enet_board_j7xevm.c

index b186c0a..f02371b 100644

--- a/packages/ti/drv/enet/examples/utils/enet_board_j7xevm.c

+++ b/packages/ti/drv/enet/examples/utils/enet_board_j7xevm.c

@@ -1313,10 +1313,11 @@ void EnetBoard_getMacAddrList(uint8_t macAddr[][ENET_MAC_ADDR_LEN],

* addresses in Linux builds. For RTOS build, MAC addresses will still

* be read from EEPROM as such I2C contention isn't an problem.

*/

+ // set static macaddr

uint8_t macAddrBuf[][ENET_MAC_ADDR_LEN] =

{

- { 0x70U, 0xFFU, 0x76U, 0x1DU, 0x92U, 0xC1U },

{ 0x70U, 0xFFU, 0x76U, 0x1DU, 0x92U, 0xC2U },

+ { 0x70U, 0xFFU, 0x76U, 0x1DU, 0x92U, 0xC1U },

{ 0x70U, 0xFFU, 0x76U, 0x1DU, 0x92U, 0xC3U },

{ 0x70U, 0xFFU, 0x76U, 0x1DU, 0x92U, 0xC4U },

{ 0x70U, 0xFFU, 0x76U, 0x1DU, 0x92U, 0xC5U },

diff --git a/packages/ti/drv/enet/src/mod/mdio.c b/packages/ti/drv/enet/src/mod/mdio.c

index fbdcead..79f0bc9 100644

--- a/packages/ti/drv/enet/src/mod/mdio.c

+++ b/packages/ti/drv/enet/src/mod/mdio.c

@@ -155,7 +155,8 @@ void Mdio_initCfg(Mdio_Cfg *mdioCfg)

mdioCfg->mdioBusFreqHz = MDIO_MDIOBUS_DFLT_FREQ_HZ;

mdioCfg->phyStatePollFreqHz = mdioCfg->mdioBusFreqHz;

mdioCfg->pollEnMask = ENET_MDIO_PHY_ADDR_MASK_ALL;

- mdioCfg->c45EnMask = ENET_MDIO_PHY_ADDR_MASK_NONE;

+ // mdioCfg->c45EnMask = ENET_MDIO_PHY_ADDR_MASK_NONE;

+ mdioCfg->c45EnMask = ENET_MDIO_PHY_ADDR_MASK_ALL;

mdioCfg->isMaster = true;

}

diff --git a/packages/ti/drv/enet/src/per/cpsw.c b/packages/ti/drv/enet/src/per/cpsw.c

index 18b0872..af1c048 100644

--- a/packages/ti/drv/enet/src/per/cpsw.c

+++ b/packages/ti/drv/enet/src/per/cpsw.c

@@ -650,6 +650,7 @@ void Cpsw_periodicTick(EnetPer_Handle hPer)

if (hPhy != NULL)

{

/* Run PHY tick */

+ // ENETTRACE_ERR("[LXC]: Cpsw_periodicTick 222222 \n");

linkStatus = EnetPhy_tick(hPhy);

/* Handle link up/down events */

diff --git a/packages/ti/drv/enet/src/per/cpsw_tpr12.c b/packages/ti/drv/enet/src/per/cpsw_tpr12.c

index 3080ccf..6bb643d 100644

--- a/packages/ti/drv/enet/src/per/cpsw_tpr12.c

+++ b/packages/ti/drv/enet/src/per/cpsw_tpr12.c

@@ -625,6 +625,7 @@ void Cpsw_periodicTick(EnetPer_Handle hPer)

if (hPhy != NULL)

{

/* Run PHY tick */

+ // ENETTRACE_ERR("[LXC]: Cpsw_periodicTick tpr12 1111\n");

linkStatus = EnetPhy_tick(hPhy);

/* Handle link up/down events */

diff --git a/packages/ti/drv/enet/src/per/icssg.c b/packages/ti/drv/enet/src/per/icssg.c

index 2d1247f..4ad3d3a 100644

--- a/packages/ti/drv/enet/src/per/icssg.c

+++ b/packages/ti/drv/enet/src/per/icssg.c

@@ -1754,6 +1754,8 @@ void Icssg_periodicTick(EnetPer_Handle hPer)

//EnetOsal_lockMutex(hIcssg->lock);

/* Run PHY tick */

+ ENETTRACE_ERR("[LXC]: Icssg_periodicTick 333333333 \n");

+

linkStatus = EnetPhy_tick(hPhy);

/* Handle link up/down events */

diff --git a/packages/ti/drv/enet/src/phy/enetphy.c b/packages/ti/drv/enet/src/phy/enetphy.c

index 43a70bc..5ac6b11 100644

--- a/packages/ti/drv/enet/src/phy/enetphy.c

+++ b/packages/ti/drv/enet/src/phy/enetphy.c

@@ -118,8 +118,6 @@ static void EnetPhy_defaultState(EnetPhy_Handle hPhy);

static void EnetPhy_findingState(EnetPhy_Handle hPhy);

-static void EnetPhy_findingState(EnetPhy_Handle hPhy);

-

static void EnetPhy_foundState(EnetPhy_Handle hPhy);

static void EnetPhy_resetWaitState(EnetPhy_Handle hPhy);

@@ -363,6 +361,7 @@ void EnetPhy_close(EnetPhy_Handle hPhy)

EnetPhy_releaseHandle(hPhy);

}

+extern void ACD_test(EnetPhy_Handle hPhy);

EnetPhy_LinkStatus EnetPhy_tick(EnetPhy_Handle hPhy)

{

EnetPhy_State *state = &hPhy->state;

@@ -370,6 +369,15 @@ EnetPhy_LinkStatus EnetPhy_tick(EnetPhy_Handle hPhy)

EnetPhy_FsmState currFsmState;

EnetPhy_LinkStatus status;

+ // static int x_count = 1;

+

+ // printf("EnetPhy_tick test ^^^^^ i=0x%x, addr=%x, state->fsmState= %d\n", x_count, hPhy->addr, state->fsmState);

+ // if (x_count % 100 == 0) {

+ // ACD_test(hPhy);

+ // }

+ // if (x_count < 0xffffffff)

+ // x_count++;

+

/* TODO: Check if pending state transitions needs to be applied,

* i.e. from EnetPhy_setPhyMode() */

@@ -514,7 +522,8 @@ bool EnetPhy_isAlive(EnetPhy_Handle hPhy)

else

{

/* Alternatively, read BMSR - PHY is alive if transaction is successful */

- status = hMdio->readC22(phyGroup, phyAddr, PHY_BMSR, &val, hPhy->mdioArgs);

+ // status = hMdio->readC22(phyGroup, phyAddr, PHY_BMSR, &val, hPhy->mdioArgs);

+ status = hMdio->readC45(phyGroup, phyAddr, 1, PHY_BMSR, &val, hPhy->mdioArgs);

ENETTRACE_ERR_IF(status != ENETPHY_SOK,

"PHY %u: Failed to read reg %u: %d\n", phyAddr, PHY_BMSR, status);

if (status == ENETPHY_SOK)

@@ -601,6 +610,7 @@ int32_t EnetPhy_getLinkCfg(EnetPhy_Handle hPhy,

return status;

}

+extern int g_DEVAD;

int32_t EnetPhy_readReg(EnetPhy_Handle hPhy,

uint32_t reg,

uint16_t *val)

@@ -610,12 +620,17 @@ int32_t EnetPhy_readReg(EnetPhy_Handle hPhy,

uint32_t phyAddr = hPhy->addr;

int32_t status;

- status = hMdio->readC22(phyGroup, phyAddr, reg, val, hPhy->mdioArgs);

+ // printf("[LXC]: EnetPhy_readReg . phyAddr = %d\n", phyAddr);

+

+ // status = hMdio->readC22(phyGroup, phyAddr, reg, val, hPhy->mdioArgs);

+ status = hMdio->readC45(phyGroup, phyAddr, g_DEVAD, reg, val, hPhy->mdioArgs);

ENETTRACE_ERR_IF(status != ENETPHY_SOK,

"PHY %u: Failed to read reg %u: %d\n", phyAddr, reg, status);

ENETTRACE_VERBOSE_IF(status == ENETPHY_SOK,

"PHY %u: reg %u val 0x%04x %s\n", phyAddr, reg, *val);

+ // printf("[LXC]: EnetPhy_readReg . status = %d\n", status);

+

return status;

}

@@ -628,7 +643,8 @@ int32_t EnetPhy_writeReg(EnetPhy_Handle hPhy,

uint32_t phyAddr = hPhy->addr;

int32_t status;

- status = hMdio->writeC22(phyGroup, phyAddr, reg, val, hPhy->mdioArgs);

+ // status = hMdio->writeC22(phyGroup, phyAddr, reg, val, hPhy->mdioArgs);

+ status = hMdio->writeC45(phyGroup, phyAddr, g_DEVAD, reg, val, hPhy->mdioArgs);

ENETTRACE_ERR_IF(status != ENETPHY_SOK,

"PHY %u: Failed to write reg %u: %d\n", phyAddr, reg, status);

ENETTRACE_VERBOSE_IF(status == ENETPHY_SOK,

@@ -648,7 +664,8 @@ int32_t EnetPhy_rmwReg(EnetPhy_Handle hPhy,

int32_t status;

uint16_t data = 0U;

- status = hMdio->readC22(phyGroup, phyAddr, reg, &data, hPhy->mdioArgs);

+ // status = hMdio->readC22(phyGroup, phyAddr, reg, &data, hPhy->mdioArgs);

+ status = hMdio->readC45(phyGroup, phyAddr, g_DEVAD, reg, &data, hPhy->mdioArgs);

ENETTRACE_ERR_IF(status != ENETPHY_SOK,

"PHY %u: Failed to read reg %u: %d\n", phyAddr, reg, status);

ENETTRACE_VERBOSE_IF(status == ENETPHY_SOK,

@@ -658,7 +675,8 @@ int32_t EnetPhy_rmwReg(EnetPhy_Handle hPhy,

{

data = (data & ~mask) | (val & mask);

- status = hMdio->writeC22(phyGroup, phyAddr, reg, data, hPhy->mdioArgs);

+ // status = hMdio->writeC22(phyGroup, phyAddr, reg, data, hPhy->mdioArgs);

+ status = hMdio->writeC45(phyGroup, phyAddr, 1, reg, data, hPhy->mdioArgs);

ENETTRACE_ERR_IF(status != ENETPHY_SOK,

"PHY %u: Failed to write reg %u: %d\n", phyAddr, reg, status);

ENETTRACE_VERBOSE_IF(status == ENETPHY_SOK,

@@ -1074,7 +1092,7 @@ static void EnetPhy_enableState(EnetPhy_Handle hPhy)

{

/* Set PHY in normal mode */

ENETTRACE_DBG("PHY %u: enable\n", hPhy->addr);

- EnetPhy_rmwReg(hPhy, PHY_BMCR, BMCR_ISOLATE | BMCR_PWRDOWN, 0U);

+ // EnetPhy_rmwReg(hPhy, PHY_BMCR, BMCR_ISOLATE | BMCR_PWRDOWN, 0U);

/* PHY-specific 'extended' configuration */

if ((hPhy->hDrv->config != NULL) &&

@@ -1198,11 +1216,11 @@ static void EnetPhy_setupNway(EnetPhy_Handle hPhy)

nway1000Advertise |= GIGCR_1000HD;

}

- EnetPhy_rmwReg(hPhy, PHY_ANAR, ANAR_100 | ANAR_10, nwayAdvertise);

+ // EnetPhy_rmwReg(hPhy, PHY_ANAR, ANAR_100 | ANAR_10, nwayAdvertise);

if ((state->phyLinkCaps & ENETPHY_LINK_CAP_1000) != 0U)

{

- EnetPhy_rmwReg(hPhy, PHY_GIGCR, GIGCR_1000, nway1000Advertise);

+ ;// EnetPhy_rmwReg(hPhy, PHY_GIGCR, GIGCR_1000, nway1000Advertise);

}

state->needsNwayCfg = false;

@@ -1210,12 +1228,12 @@ static void EnetPhy_setupNway(EnetPhy_Handle hPhy)

/* Restart auto-negotiation */

ENETTRACE_DBG("PHY %u: restart autonegotiation\n", hPhy->addr);

- EnetPhy_rmwReg(hPhy, PHY_BMCR, BMCR_ANEN, BMCR_ANEN);

+ // EnetPhy_rmwReg(hPhy, PHY_BMCR, BMCR_ANEN, BMCR_ANEN);

/* TODO: is MII_ENETPHY_FD needed for auto-negotiation? */

- EnetPhy_rmwReg(hPhy, PHY_BMCR,

- BMCR_ANRESTART | BMCR_FD,

- BMCR_ANRESTART | BMCR_FD);

+ // EnetPhy_rmwReg(hPhy, PHY_BMCR,

+ // BMCR_ANRESTART | BMCR_FD,

+ // BMCR_ANRESTART | BMCR_FD);

}

static void EnetPhy_setupManual(EnetPhy_Handle hPhy,

@@ -1292,16 +1310,27 @@ static void EnetPhy_setupManual(EnetPhy_Handle hPhy,

hPhy->addr, EnetPhy_getModeString(state->speed, state->duplexity));

}

+extern int g_DEVAD;

static void EnetPhy_loopbackState(EnetPhy_Handle hPhy)

{

bool loopback = false;

int32_t status;

- uint16_t val;

+ // uint16_t val;

+ uint16_t val1, val2;

+

+ g_DEVAD = 0x03;

+ status = EnetPhy_readReg(hPhy, 0x0000, &val1);

+ g_DEVAD = 0x01;

+ status = EnetPhy_readReg(hPhy, 0x0000, &val2);

- status = EnetPhy_readReg(hPhy, PHY_BMCR, &val);

+ // status = EnetPhy_readReg(hPhy, PHY_BMCR, &val);

if (status == ENETPHY_SOK)

{

- loopback = ((val & BMCR_LOOPBACK) != 0U);

+ // loopback = ((val & BMCR_LOOPBACK) != 0U);

+ if (val2 & 0x1 != 0 || val1 & 0x4000 != 0) {

+ EnetUtils_printf("[xujibin] %s:%d lookback true\n", __FUNCTION__, __LINE__);

+ loopback = true;

+ }

}

else

{

@@ -1325,6 +1354,7 @@ static void EnetPhy_nwayStartState(EnetPhy_Handle hPhy)

/* Wait for NWAY to start */

EnetPhy_readReg(hPhy, PHY_BMCR, &mode);

+ mode |= BMCR_ANRESTART;

if ((mode & BMCR_ANRESTART) == 0U)

{

@@ -1355,6 +1385,8 @@ static void EnetPhy_nwayWaitState(EnetPhy_Handle hPhy)

"PHY %u: unexpected state for strapped PHY\n", hPhy->addr);

EnetPhy_readReg(hPhy, PHY_BMSR, &status);

+ status |= BMSR_ANCOMPLETE;

+ status |= BMSR_LINKSTS;

if (0U != (status & BMSR_ANCOMPLETE))

{

nwayCaps = EnetPhy_findCommonNwayCaps(hPhy);

@@ -1396,6 +1428,7 @@ static void EnetPhy_linkWaitState(EnetPhy_Handle hPhy)

EnetPhy_readReg(hPhy, PHY_BMSR, &status);

+ status |= BMSR_LINKSTS;

if ((status & BMSR_LINKSTS) != 0U)

{

/* Populate FSM state now as most FSM states are bypassed for strapped PHYs */

@@ -1450,59 +1483,77 @@ static void EnetPhy_linkedState(EnetPhy_Handle hPhy)

static bool EnetPhy_isNwayCapable(EnetPhy_Handle hPhy)

{

- uint16_t val = 0U;

+ // uint16_t val = 0U;

/* Get the PHY Status */

- EnetPhy_readReg(hPhy, PHY_BMSR, &val);

+ // EnetPhy_readReg(hPhy, PHY_BMSR, &val);

- return ((val & BMSR_ANCAPABLE) != 0U);

+ // return ((val & BMSR_ANCAPABLE) != 0U);

+ return true;

}

+extern int g_speed;

static uint32_t EnetPhy_getLocalCaps(EnetPhy_Handle hPhy)

{

uint32_t caps = 0U;

- uint16_t val = 0U;

- /* Get 10/100 Mbps capabilities */

- EnetPhy_readReg(hPhy, PHY_BMSR, &val);

- if ((val & BMSR_100FD) != 0U)

- {

- caps |= ENETPHY_LINK_CAP_FD100;

- }

-

- if ((val & BMSR_100HD) != 0U)

- {

- caps |= ENETPHY_LINK_CAP_HD100;

- }

-

- if ((val & BMSR_10FD) != 0U)

- {

- caps |= ENETPHY_LINK_CAP_FD10;

- }

-

- if ((val & BMSR_10HD) != 0U)

- {

- caps |= ENETPHY_LINK_CAP_HD10;

- }

-

- /* Get extended (1 Gbps) capabilities if supported */

- if ((val & BMSR_GIGEXTSTS) != 0U)

- {

- EnetPhy_readReg(hPhy, PHY_GIGESR, &val);

-

- if ((val & GIGESR_1000FD) != 0U)

- {

- caps |= ENETPHY_LINK_CAP_FD1000;

- }

-

- if ((val & GIGESR_1000HD) != 0U)

- {

- caps |= ENETPHY_LINK_CAP_HD1000;

- }

+ /* Get 10/100/1000 Mbps capabilities */

+ caps |= ENETPHY_LINK_CAP_FD100;

+ caps |= ENETPHY_LINK_CAP_HD100;

+ caps |= ENETPHY_LINK_CAP_FD10;

+ caps |= ENETPHY_LINK_CAP_HD10;

+ if (g_speed == 1000) {

+ caps |= ENETPHY_LINK_CAP_FD1000;

+ caps |= ENETPHY_LINK_CAP_HD1000;

}

return caps;

}

+// static uint32_t EnetPhy_getLocalCaps(EnetPhy_Handle hPhy)

+// {

+// uint32_t caps = 0U;

+// // uint16_t val = 0U;

+

+// /* Get 10/100 Mbps capabilities */

+// EnetPhy_readReg(hPhy, PHY_BMSR, &val);

+// if ((val & BMSR_100FD) != 0U)

+// {

+// caps |= ENETPHY_LINK_CAP_FD100;

+// }

+

+// if ((val & BMSR_100HD) != 0U)

+// {

+// caps |= ENETPHY_LINK_CAP_HD100;

+// }

+

+// if ((val & BMSR_10FD) != 0U)

+// {

+// caps |= ENETPHY_LINK_CAP_FD10;

+// }

+

+// if ((val & BMSR_10HD) != 0U)

+// {

+// caps |= ENETPHY_LINK_CAP_HD10;

+// }

+

+// /* Get extended (1 Gbps) capabilities if supported */

+// if ((val & BMSR_GIGEXTSTS) != 0U)

+// {

+// EnetPhy_readReg(hPhy, PHY_GIGESR, &val);

+

+// if ((val & GIGESR_1000FD) != 0U)

+// {

+// caps |= ENETPHY_LINK_CAP_FD1000;

+// }

+

+// if ((val & GIGESR_1000HD) != 0U)

+// {

+// caps |= ENETPHY_LINK_CAP_HD1000;

+// }

+// }

+

+// return caps;

+// }

static uint32_t EnetPhy_findCommonCaps(EnetPhy_Handle hPhy)

{

@@ -1513,49 +1564,58 @@ static uint32_t EnetPhy_findCommonCaps(EnetPhy_Handle hPhy)

/* Get local device capabilities */

EnetPhy_readReg(hPhy, PHY_ANAR, &val);

- if ((val & ANAR_100FD) != 0U)

- {

- localCaps |= ENETPHY_LINK_CAP_FD100;

- }

+ // if ((val & ANAR_100FD) != 0U)

+ // {

+ // localCaps |= ENETPHY_LINK_CAP_FD100;

+ // }

- if ((val & ANAR_100HD) != 0U)

- {

- localCaps |= ENETPHY_LINK_CAP_HD100;

- }

+ // if ((val & ANAR_100HD) != 0U)

+ // {

+ // localCaps |= ENETPHY_LINK_CAP_HD100;

+ // }

- if ((val & ANAR_10FD) != 0U)

- {

- localCaps |= ENETPHY_LINK_CAP_FD10;

- }

+ // if ((val & ANAR_10FD) != 0U)

+ // {

+ // localCaps |= ENETPHY_LINK_CAP_FD10;

+ // }

- if ((val & ANAR_10HD) != 0U)

- {

- localCaps |= ENETPHY_LINK_CAP_HD10;

- }

+ // if ((val & ANAR_10HD) != 0U)

+ // {

+ // localCaps |= ENETPHY_LINK_CAP_HD10;

+ // }

+

+ localCaps |= ENETPHY_LINK_CAP_FD100;

+ localCaps |= ENETPHY_LINK_CAP_HD100;

+ localCaps |= ENETPHY_LINK_CAP_FD10;

+ localCaps |= ENETPHY_LINK_CAP_HD10;

/* Get link partner capabilities */

val = 0U;

EnetPhy_readReg(hPhy, PHY_ANLPAR, &val);

- if ((val & ANLPAR_100FD) != 0U)

- {

- partnerCaps |= ENETPHY_LINK_CAP_FD100;

- }

-

- if ((val & ANLPAR_100HD) != 0U)

- {

- partnerCaps |= ENETPHY_LINK_CAP_HD100;

- }

-

- if ((val & ANLPAR_10FD) != 0U)

- {

- partnerCaps |= ENETPHY_LINK_CAP_FD10;

- }

-

- if ((val & ANLPAR_10HD) != 0U)

- {

- partnerCaps |= ENETPHY_LINK_CAP_HD10;

- }

+ // if ((val & ANLPAR_100FD) != 0U)

+ // {

+ // partnerCaps |= ENETPHY_LINK_CAP_FD100;

+ // }

+

+ // if ((val & ANLPAR_100HD) != 0U)

+ // {

+ // partnerCaps |= ENETPHY_LINK_CAP_HD100;

+ // }

+

+ // if ((val & ANLPAR_10FD) != 0U)

+ // {

+ // partnerCaps |= ENETPHY_LINK_CAP_FD10;

+ // }

+

+ // if ((val & ANLPAR_10HD) != 0U)

+ // {

+ // partnerCaps |= ENETPHY_LINK_CAP_HD10;

+ // }

+ partnerCaps |= ENETPHY_LINK_CAP_FD100;

+ partnerCaps |= ENETPHY_LINK_CAP_HD100;

+ partnerCaps |= ENETPHY_LINK_CAP_FD10;

+ partnerCaps |= ENETPHY_LINK_CAP_HD10;

ENETTRACE_DBG("PHY %u: local caps: %s\n",

hPhy->addr, EnetPhy_getCapsString(localCaps));

@@ -1571,41 +1631,47 @@ static uint32_t EnetPhy_findCommon1000Caps(EnetPhy_Handle hPhy)

{

uint32_t localCaps = 0U;

uint32_t partnerCaps = 0U;

- uint16_t val;

-

- /* Get local device capabilities */

- EnetPhy_readReg(hPhy, PHY_GIGCR, &val);

-

- if ((val & GIGCR_1000FD) != 0U)

- {

+ // uint16_t val;

+

+ // /* Get local device capabilities */

+ // EnetPhy_readReg(hPhy, PHY_GIGCR, &val);

+

+ // if ((val & GIGCR_1000FD) != 0U)

+ // {

+ // localCaps |= ENETPHY_LINK_CAP_FD1000;

+ // }

+

+ // if ((val & GIGCR_1000HD) != 0U)

+ // {

+ // localCaps |= ENETPHY_LINK_CAP_HD1000;

+ // }

+

+ // /* Get link partner capabilities */

+ // EnetPhy_readReg(hPhy, PHY_GIGSR, &val);

+

+ // if ((val & GIGSR_1000FD) != 0U)

+ // {

+ // partnerCaps |= ENETPHY_LINK_CAP_FD1000;

+ // }

+

+ // if ((val & GIGSR_1000FD) != 0U)

+ // {

+ // partnerCaps |= ENETPHY_LINK_CAP_HD1000;

+ // }

+

+ // ENETTRACE_DBG("PHY %u: local caps: %s\n",

+ // hPhy->addr, EnetPhy_getCapsString(localCaps));

+ // ENETTRACE_DBG("PHY %u: partner caps: %s\n",

+ // hPhy->addr, EnetPhy_getCapsString(partnerCaps));

+ // ENETTRACE_DBG("PHY %u: common caps: %s\n",

+ // hPhy->addr, EnetPhy_getCapsString(localCaps & partnerCaps));

+

+ if (g_speed == 1000) {

localCaps |= ENETPHY_LINK_CAP_FD1000;

- }

-

- if ((val & GIGCR_1000HD) != 0U)

- {

localCaps |= ENETPHY_LINK_CAP_HD1000;

- }

-

- /* Get link partner capabilities */

- EnetPhy_readReg(hPhy, PHY_GIGSR, &val);

-

- if ((val & GIGSR_1000FD) != 0U)

- {

partnerCaps |= ENETPHY_LINK_CAP_FD1000;

- }

-

- if ((val & GIGSR_1000FD) != 0U)

- {

partnerCaps |= ENETPHY_LINK_CAP_HD1000;

}

-

- ENETTRACE_DBG("PHY %u: local caps: %s\n",

- hPhy->addr, EnetPhy_getCapsString(localCaps));

- ENETTRACE_DBG("PHY %u: partner caps: %s\n",

- hPhy->addr, EnetPhy_getCapsString(partnerCaps));

- ENETTRACE_DBG("PHY %u: common caps: %s\n",

- hPhy->addr, EnetPhy_getCapsString(localCaps & partnerCaps));

-

return (localCaps & partnerCaps);

}

@@ -1640,6 +1706,7 @@ static uint32_t EnetPhy_findCommonNwayCaps(EnetPhy_Handle hPhy)

return nwayCaps;

}

+extern int g_loopback;

static bool EnetPhy_isPhyLinked(EnetPhy_Handle hPhy)

{

EnetPhy_MdioHandle hMdio = hPhy->hMdio;

@@ -1649,6 +1716,9 @@ static bool EnetPhy_isPhyLinked(EnetPhy_Handle hPhy)

uint16_t val = 0U;

int32_t status;

+ if (g_loopback == 1)

+ return true;

+

/* Get PHY link status */

if (hMdio->isLinked != NULL)

{

@@ -1660,7 +1730,8 @@ static bool EnetPhy_isPhyLinked(EnetPhy_Handle hPhy)

else

{

/* Alternatively, BMSR[2] Link Status bit can be checked */

- status = hMdio->readC22(phyGroup, phyAddr, PHY_BMSR, &val, hPhy->mdioArgs);

+ // status = hMdio->readC22(phyGroup, phyAddr, PHY_BMSR, &val, hPhy->mdioArgs);

+ status = hMdio->readC45(phyGroup, phyAddr, 1, PHY_BMSR, &val, hPhy->mdioArgs);

ENETTRACE_ERR_IF(status != ENETPHY_SOK,

"PHY %u: Failed to read reg %u: %d\n", phyAddr, PHY_BMSR, status);

if ((status == ENETPHY_SOK) &&

diff --git a/packages/ti/drv/enet/src/phy/generic_phy.c b/packages/ti/drv/enet/src/phy/generic_phy.c

index 21200cb..1d3534c 100644

--- a/packages/ti/drv/enet/src/phy/generic_phy.c

+++ b/packages/ti/drv/enet/src/phy/generic_phy.c

@@ -50,6 +50,9 @@

#include "enetphy_priv.h"

#include "generic_phy.h"

+#include <ti/drv/i2c/I2C.h>

+#include <stdio.h>

+

/* ========================================================================== */

/* Macros & Typedefs */

/* ========================================================================== */

@@ -72,6 +75,8 @@ static bool GenericPhy_isPhyDevSupported(EnetPhy_Handle hPhy,

static bool GenericPhy_isMacModeSupported(EnetPhy_Handle hPhy,

EnetPhy_Mii mii);

+static void Bcm89881_config(EnetPhy_Handle hPhy);

+

/* ========================================================================== */

/* Global Variables */

/* ========================================================================== */

@@ -92,6 +97,88 @@ EnetPhy_Drv gEnetPhyDrvGeneric =

/* ========================================================================== */

/* Function Definitions */

/* ========================================================================== */

+#define TCA6424_CMD_AUTO_INC ((uint8_t) 0x80U)

+

+/* Input status register */

+#define TCA6424_REG_INPUT0 ((UInt8) 0x00U)

+#define TCA6424_REG_INPUT1 ((UInt8) 0x01U)

+#define TCA6424_REG_INPUT2 ((UInt8) 0x02U)

+

+/* Output register to change state of output BIT set to 1, output set HIGH */

+#define TCA6424_REG_OUTPUT0 ((uint8_t) 0x04U)

+#define TCA6424_REG_OUTPUT1 ((uint8_t) 0x05U)

+#define TCA6424_REG_OUTPUT2 ((uint8_t) 0x06U)

+

+/* Configuration register. BIT = '1' sets port to input, BIT = '0' sets

+ * port to output */

+#define TCA6424_REG_CONFIG0 ((uint8_t) 0x0CU)

+#define TCA6424_REG_CONFIG1 ((uint8_t) 0x0DU)

+#define TCA6424_REG_CONFIG2 ((uint8_t) 0x0EU)

+

+void SetupI2CTransfer(I2C_Handle handle, uint32_t slaveAddr,

+ uint8_t *writeData, uint32_t numWriteBytes,

+ uint8_t *readData, uint32_t numReadBytes)

+{

+ bool status;

+ I2C_Transaction i2cTransaction;

+

+ printf("\n[LXC]: SetupI2CTransfer start. \n");

+ I2C_transactionInit(&i2cTransaction);

+ i2cTransaction.slaveAddress = slaveAddr;

+ i2cTransaction.writeBuf = (uint8_t *)&writeData[0];

+ i2cTransaction.writeCount = numWriteBytes;

+ i2cTransaction.readBuf = (uint8_t *)&readData[0];

+ i2cTransaction.readCount = numReadBytes;

+ status = I2C_transfer(handle, &i2cTransaction);

+ if(FALSE == status)

+ {

+ printf("\n Data Transfer failed. \n");

+ }

+ printf("\n[LXC]: SetupI2CTransfer end. \n");

+}

+extern void Board_delay(uint32_t delayCycles);

+void Bcm89881_init(EnetPhy_Handle hPhy)

+{

+ I2C_Params i2cParams;

+ I2C_Handle handle = NULL;

+ uint8_t dataToSlave[4];

+

+ /*

+ * Configuring TCA6424 IO Exp 2 with addr 0x22

+ * This io expander is controlled by i2c0

+ */

+ /* I2C initialization */

+ printf("\n[LXC]: Bcm89881_init start. \n");

+ I2C_init();

+ I2C_Params_init(&i2cParams);

+ i2cParams.transferMode = I2C_MODE_BLOCKING;

+ i2cParams.bitRate = I2C_400kHz;

+ i2cParams.transferCallbackFxn = NULL;

+

+ handle = I2C_open(0U, &i2cParams);

+

+printf("\n[LXC]: Bcm89881_init ing 11111. \n");

+ dataToSlave[0] = TCA6424_REG_CONFIG0 | TCA6424_CMD_AUTO_INC;

+ dataToSlave[1] = 0x0U;

+ SetupI2CTransfer(handle, 0x22, &dataToSlave[0], 2, NULL, 0);

+printf("\n[LXC]: Bcm89881_init ing 22222. \n");

+

+ dataToSlave[0] = TCA6424_REG_INPUT0 | TCA6424_CMD_AUTO_INC;

+ dataToSlave[1] = 0x0U;

+ dataToSlave[2] = 0x0U;

+ dataToSlave[3] = 0x0U;

+ SetupI2CTransfer(handle, 0x22, &dataToSlave[0], 1, &dataToSlave[1], 3);

+printf("\n[LXC]: Bcm89881_init ing 33333. \n");

+

+ /* Set P20 to 0. Delay 22, and Set to 1;

+ */

+ Board_delay(22);

+ dataToSlave[0] = TCA6424_REG_OUTPUT2;

+ dataToSlave[1] |= 0x1;

+ SetupI2CTransfer(handle, 0x22, &dataToSlave[0], 1, &dataToSlave[1], 1);

+ printf("\n[LXC]: Bcm89881_init Stop. \n");

+

+}

static bool GenericPhy_isPhyDevSupported(EnetPhy_Handle hPhy,

const EnetPhy_Version *version)

@@ -112,7 +199,10 @@ void GenericPhy_reset(EnetPhy_Handle hPhy)

ENETTRACE_DBG("PHY %u: reset\n", hPhy->addr);

/* Reset the PHY */

- EnetPhy_rmwReg(hPhy, PHY_BMCR, BMCR_RESET, BMCR_RESET);

+ // EnetPhy_rmwReg(hPhy, PHY_BMCR, BMCR_RESET, BMCR_RESET);

+ printf("\n[LXC]: GenericPhy_reset. PHY %u: reset \n", hPhy->addr);

+

+ Bcm89881_config(hPhy);

}

bool GenericPhy_isResetComplete(EnetPhy_Handle hPhy)

@@ -137,65 +227,72 @@ int32_t GenericPhy_readExtReg(EnetPhy_Handle hPhy,

uint32_t reg,

uint16_t *val)

{

- uint16_t devad = MMD_CR_DEVADDR;

- int32_t status;

+ // uint16_t devad = MMD_CR_DEVADDR;

+ // int32_t status;

- status = EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_ADDR);

+ // status = EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_ADDR);

- if (status == ENETPHY_SOK)

- {

- status = EnetPhy_writeReg(hPhy, PHY_MMD_DR, reg);

- }

+ // if (status == ENETPHY_SOK)

+ // {

+ // status = EnetPhy_writeReg(hPhy, PHY_MMD_DR, reg);

+ // }

- if (status == ENETPHY_SOK)

- {

- EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_DATA_NOPOSTINC);

- }

+ // if (status == ENETPHY_SOK)

+ // {

+ // EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_DATA_NOPOSTINC);

+ // }

- if (status == ENETPHY_SOK)

- {

- status = EnetPhy_readReg(hPhy, PHY_MMD_DR, val);

- }

+ // if (status == ENETPHY_SOK)

+ // {

+ // status = EnetPhy_readReg(hPhy, PHY_MMD_DR, val);

+ // }

- ENETTRACE_VERBOSE_IF(status == ENETPHY_SOK,

- "PHY %u: failed to read reg %u\n", hPhy->addr, reg);

- ENETTRACE_ERR_IF(status != ENETPHY_SOK,

- "PHY %u: read reg %u val 0x%04x\n", hPhy->addr, reg, *val);

+ // ENETTRACE_VERBOSE_IF(status == ENETPHY_SOK,

+ // "PHY %u: failed to read reg %u\n", hPhy->addr, reg);

+ // ENETTRACE_ERR_IF(status != ENETPHY_SOK,

+ // "PHY %u: read reg %u val 0x%04x\n", hPhy->addr, reg, *val);

- return status;

+ // return status;

+ return ENETPHY_SOK;

}

int32_t GenericPhy_writeExtReg(EnetPhy_Handle hPhy,

uint32_t reg,

uint16_t val)

{

- uint16_t devad = MMD_CR_DEVADDR;

- int32_t status;

+ // uint16_t devad = MMD_CR_DEVADDR;

+ // int32_t status;

- ENETTRACE_VERBOSE("PHY %u: write %u val 0x%04x\n", hPhy->addr, reg, val);

+ // ENETTRACE_VERBOSE("PHY %u: write %u val 0x%04x\n", hPhy->addr, reg, val);

- status = EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_ADDR);

- if (status == ENETPHY_SOK)

- {

- EnetPhy_writeReg(hPhy, PHY_MMD_DR, reg);

- }

+ // status = EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_ADDR);

+ // if (status == ENETPHY_SOK)

+ // {

+ // EnetPhy_writeReg(hPhy, PHY_MMD_DR, reg);

+ // }

- if (status == ENETPHY_SOK)

- {

- EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_DATA_NOPOSTINC);

- }

+ // if (status == ENETPHY_SOK)

+ // {

+ // EnetPhy_writeReg(hPhy, PHY_MMD_CR, devad | MMD_CR_DATA_NOPOSTINC);

+ // }

- if (status == ENETPHY_SOK)

- {

- EnetPhy_writeReg(hPhy, PHY_MMD_DR, val);

- }

+ // if (status == ENETPHY_SOK)

+ // {

+ // EnetPhy_writeReg(hPhy, PHY_MMD_DR, val);

+ // }

- ENETTRACE_ERR_IF(status != ENETPHY_SOK,

- "PHY %u: failed to write reg %u val 0x%04x\n", hPhy->addr, reg, val);

+ // ENETTRACE_ERR_IF(status != ENETPHY_SOK,

+ // "PHY %u: failed to write reg %u val 0x%04x\n", hPhy->addr, reg, val);

- return status;

+ // return status;

+ return ENETPHY_SOK;

}

+

+// void thoumaster(EnetPhy_Handle hPhy);

+// void thouslave(EnetPhy_Handle hPhy);

+// void hunmaster(EnetPhy_Handle hPhy);

+// void hunslave(EnetPhy_Handle hPhy);

void GenericPhy_printRegs(EnetPhy_Handle hPhy)

{

uint32_t i;

@@ -207,3 +304,542 @@ void GenericPhy_printRegs(EnetPhy_Handle hPhy)

EnetUtils_printf("PHY %u: reg 0x%02x = 0x%04x\n", hPhy->addr, i, val);

}

}

+

+/* phy config */

+int g_master = 1;

+int g_speed = 100;

+int g_loopback = 0;

+/* end of phy config */

+

+int g_DEVAD = 1;

+// static void Bcm89881_config(EnetPhy_Handle hPhy)

+// {

+// EnetUtils_printf("Bcm89881_config start, master:%d, speed:%d, loopback:%d\n",

+// g_master, g_speed, g_loopback);

+

+// /* master mode */

+// if (g_master) {

+// if (g_speed == 1000)

+// thoumaster(hPhy);

+// else if (g_speed == 100)

+// hunmaster(hPhy);

+// return;

+// }

+

+// /* slave mode */

+// if (g_speed == 1000)

+// thouslave(hPhy);

+// else if (g_speed == 100)

+// hunslave(hPhy);

+// }

+

+static void thouslave(EnetPhy_Handle hPhy)

+{

+ g_DEVAD = 0x01;

+

+ EnetPhy_writeReg(hPhy, 0x0000, 0x8040); // 'reset