- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

It is mentioned in the AM6442 errata sheet that the SERDES_REFCLK cannot be used as PCIe REFCLK output. However, it is used as PCIe REFCLK output in the Evaluation Board and PCIe devices are working fine in that. So, is it okay to use the SERDES_REFCLK as PCIe REFCLK output? I am really confused. I will be connecting a Cyclone IV GX FPGA to the SoC and it will be using a PCIe Gen2 x1 interface.

Hi Biju,

maybe this entry answers your question.

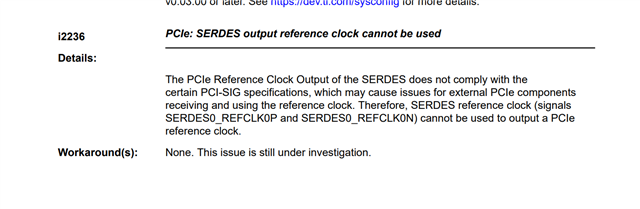

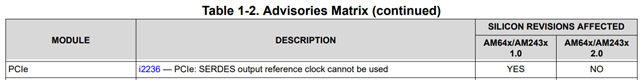

AM6442: Errata i2236 PCIe: SERDES output reference clock cannot be used

Armin

Thanks Armin!

Biju,

As outlined in the erratum, the REFCLK for Revision1 of the device is non-compliant in certain circumstances. As you have seen in your testing, in many cases this doesn't translate into a failure of the interface itself, but given that PCIe is an industry standard and we can't test against every device in existence, there does exist the possibility that any spec deviation could cause some attached devices to fail.

Thanks, Armin and DK,

So, I am planning to put an external clock source as an assembly option that can be used if in case the SoC REFCLK gives any issues. Whether TI has any recommendations for the same?

Hi,

The engineer responsible for this returns tomorrow. I should have an answer for you then.

Hi All

Please refer below update from the device expert

If you/customer are asking if the AM64x 100MHz PCIe REFCLK can be sourced from the SoC, the answer is “yes” for PG2 (but ”no” for PG1). This clock was fully qualified to meet the PCIe REFCLK standard on PG2.

Regards,

Sreenivasa