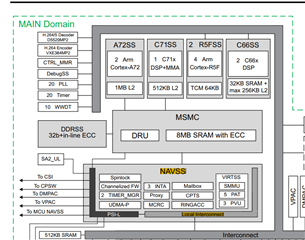

Other Parts Discussed in Thread: DRA829, , SYSBIOS

Hi,

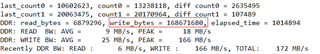

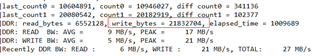

I want to monitor DDR bankwidth (sdk7.1) by ctoolslib_J721E_DRA829_TDA4VM_v0.2 .

How to implement CTools lib's source code to a part of the Linux os? I try to run prebuild tool example_ddr_cpt2_tbr.a72.out on a72 linux, but it failed

root@j7-evm:/mnt# ./example_ddr_cpt2_tbr.a72.out Illegal instruction

root@j7-evm:/mnt# ./ddr_test Opening CPT2 probe... Segmentation fault