Hi TI experts,

When I was executing the application, the following problems occurred,

test_app is --> ./vx_app_conformance.out --filter=tivxHwaVideoEncoder.SingleStreamProcessing

The application is stuck,The printing information is as follows,

root@j7-evm:/opt/vision_apps# ./vx_app_conformance.out --filter=tivxHwaVideoEncoder.SingleStreamProcessing

APP: Init ... !!!

MEM: Init ... !!!

MEM: Initialized DMA HEAP (fd=4) !!!

MEM: Init ... Done !!!

[ZHC ADDED]APP:ENABLE_IPC_MCU2_0 Init ... !!!

IPC: Init ... !!!

IPC: Init ... Done !!!

REMOTE_SERVICE: SUCCESS: register handler[0][8] for service [com.ti.module_ctrl]

REMOTE_SERVICE: Init ... !!!

REMOTE_SERVICE: Init ... Done !!!

REMOTE_SERVICE: SUCCESS: register handler[0][8] for service [com.ti.perf_stats]

APP: Init ... Done !!!

5596.669255 s: VX_ZONE_INIT:Enabled

5596.669278 s: VX_ZONE_ERROR:Enabled

5596.669285 s: VX_ZONE_WARNING:Enabled

5596.669886 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

5596.670076 s: VX_ZONE_INIT:[tivxHostInit:56] Initialization Done for HOST !!!

VxTests version: 1.1-20170301

VCS version: unknown

Build config: Release

[ ======== ] Total 22704 tests from 151 test cases

Use test filter: tivxHwaVideoEncoder.SingleStreamProcessing

Use global OpenVX context: FALSE

[ -------- ] tests from tivxHwaVideoEncoder

[ RUN 0001 ] tivxHwaVideoEncoder.SingleStreamProcessing ...

[MCU2_0] 5599.276205 s: TIMEOUT: topazdd_wait_on_sync timed out waiting for writeback 0x05a80000.

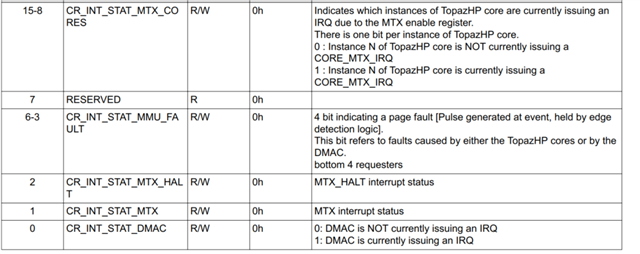

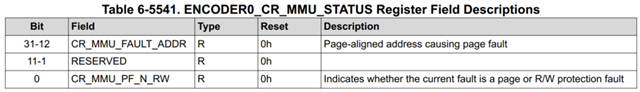

I try to analyze the source code(SDK 7.00),The function osa_irqreturn_t topazdd_isr(void * inst_data) was found to have entered the branch of “ Page fault ”,Then all interrupts were disabled.

Reg TOPAZHP_TOP_CR_MULTICORE_INT_STAT is 0x80000011

Reg TOPAZHP_TOP_CR_MMU_STATUS is 0x00000001

So please help me to locate why this problem occurs?

We also adjusted the memory layout before

modified Original file

![]()

Do the above operations cause the above problems? If so, how will we solve it?

Looking for your reply!

Best regards!