Other Parts Discussed in Thread: TDA4VM

Dear Support.

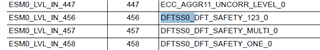

There are some 'DFTSS0_DFT_SAFETY' listed in TDA4VM TRM ( as follows). We have known that DFTSS0 was the module in PSC0, but we have no idea what the function of DFTSS0 is and what the meaning of the 'DFTSS0_DFT_SAFETY' interrupt.

Could you please provide some details for DFTSS0 or tell us which chapter describes related situation?

Thank you for your help, sincerely.