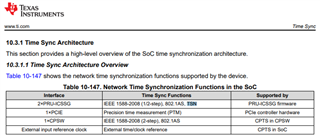

We plan to implement a platform based on AM64x, which should be able to work with both EtherCAT and TSN + OPC UA. Ports for TSN + OPC UA should work instead of EtherCAT, like a Daisy chain. According to the description, full TSN support is only available on PRU-ICSSG, but we did not find this feature in the current SDK, checking TSN on PRU-ICSSG. Maybe I didn't look carefully, are there examples in the PRU-ICSSG SDK for TSN? Do I understand correctly that the current TSN support for CPSW is limited only to the subject of the standards that are in the reference manual, and not a complete set of TSN standards on CPSW is supported? If we want a full TSN should we do on PRU-ICSSG?

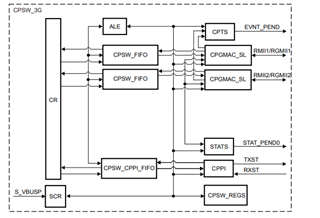

On the hardware platform, we only would like to use two physics. For EtherCAT, we will use the MII1 and MII2 pins of the PRU-ICSSG. Initially we thought that if we would like to use 2 physics we need a signal mixer for RGMII1 CPSW. Since RGMII1 CPSW does not have a complete match on MII pins PRU-ICSSG. RGMII2 pins are compatible with PRU-ICSSG MII pins.

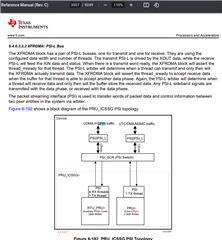

Now we are analyzing the possibility, and we need your help in the next paragraph, to use the Port Programming Interface (CPPI) port (port 0) in conjunction with the PRU-ICSSG ports.

Am I correct in understanding that the PRU-ICSSG MII or RGMII port can communicate with the CPPI port of the CPSW? Can only PRU-ICSSG ports be used to get Daisy chain for OPC UA + TSN?

Is it possible to be limited to only two physicists, without additional IC, use CPSW ports, programmatically switching between PRU-ICSSG?

At the moment, I have the following vision:

1. RGMII1 CPSW/MII PRU-ICSSG + additional chip to use only one physics.

2. RMII 2/MII PRU-ICSSG + without additional IC to use only one physics.

or

1. MII PRU-ICSSG + CPPI CPSW without additional IC to use only one physics.

2. RMII 2 / MII PRU-ICSSG + without additional IC to use only one physics.

Is the second option possible?