Other Parts Discussed in Thread: TMDSLCDK6748,

Hi Team,

Our customer is developing their system with TMS320C6748EZWT4. Customer was evaluating the Noise Immunity test with their system, they encountered the issue which their system freeze suddenly. Customer noticed there are descriptions about ESD Immunity in C6748 Errata (https://www.ti.com/lit/pdf/sprz303 : 2.1.4 System-Level ESD Immunity Usage Note). Since customer would like to understand it exactly, we received some inquires about this 2.1.4 section, as follows.

- Regarding “Figure 2. External 3.3V Clock Source”, customer understands X1 means an external oscillator. Is customer’s understanding correct?

- If so, customer wants to know what OSCOUT means. Does this mean the clock-out pin?

- For the oscillator which customer used, Customer mentioned there is not VDD, GND and Enable-pin. Customer would like to clarify this X1 device.

I believe customer is using the crystal (not oscillator). Since TI recommends external oscillator implementation for ESD robustness, I suppose we should share the information about the oscillator which TI recommends. Can I have your Expert’s advice/comments on this, please?

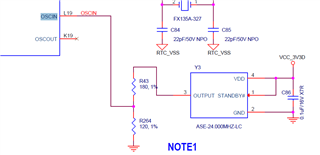

As far as I checked TMDSLCDK6748 -EVM’s schematic ( https://www.ti.com/lit/zip/sprcaf4 ), I believe the above implementation is accomplished in our EVM. Should I request customer to refer this schematic? And can I mention TI recommends ASE-24.000MHZ-LC?

Best regards,

Miyazaki