HI Ti Engineer,

TDA3x debugging problem description:

I. Hardware environment:

The design is based on the official development board drawings. The main differences are as follows:

1. The MODEL of SoC is TDA3MVRBFABFRQ1;

2, PMIC power supply changed to TPS65917 (O917A152TRGZTQ1) (official development board with LP87332ARHDRQ1 and LP87322ERHDRQ1);

3. The official development board of DDRIII design uses DDR_ECC port and chip, and we design this port as empty connection; DDRIII model used is43TR16256BL-107MBLI (official development board used model mt41K128M16JT-125)

4. QSPI FLASH is not designed to connect CLK signal back to RTCLK pin of SoC;

5. We did not use the dial switch design control Settings of SW8001 on the official development board;

Second, problem phenomenon

1. CCS download environment;

2. JTAG can be connected successfully but cannot be loaded.

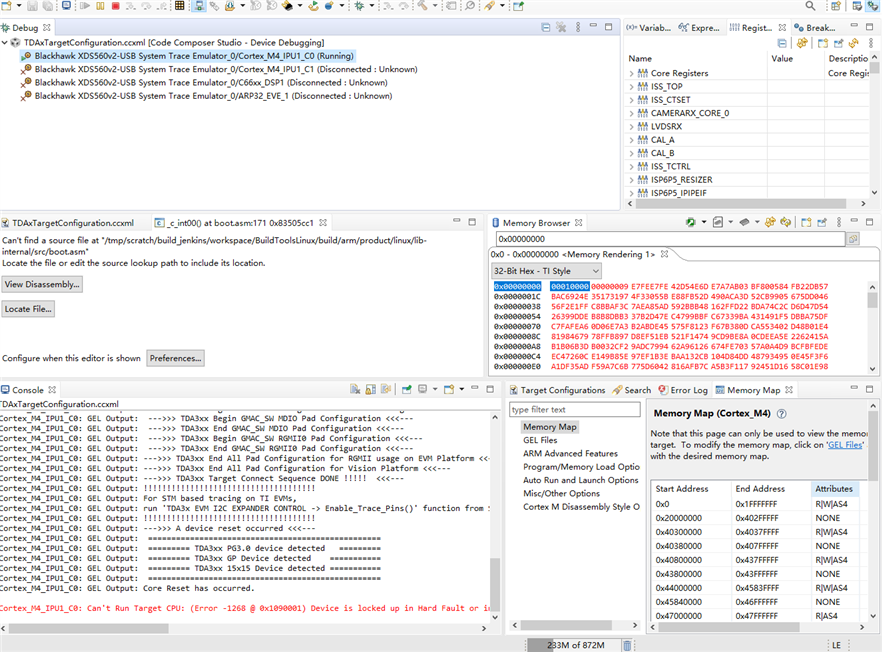

PDF according to visionsdk_userguide_tda3xx. PDF and processorsdkradar_userGuide. PDF, we want to download the firmware in QSPI mode and start TDA3x. The Blackhawk USB560v2 System Trace debugger was able to connect to the target CPU, but failed to load the.xem4 SBL file generated by the compilation:

The error log is as follows:

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence In Progress... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence DONE! <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence In Progress... <<<---

Cortex_M4_IPU1_C1: GEL Output: --->>> TDA3xx Cortex M4 Startup Sequence DONE! <<<---

ARP32_EVE_1: GEL Output: --->>> Configuring EVE Memory Map <<<---

ARP32_EVE_1: GEL Output: --->>> EVE Memory Map Done! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Target Connect Sequence Begins ... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> A device reset occurred <<<---

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx PG3.0 device detected =========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx GP Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx 15x15 Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: Core Reset has occurred.

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx PG3.0 device detected =========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx GP Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx 15x15 Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: --->>> All Control module lock registers are UNLOCKED <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> RTI is not currently enabled, so not doing anything <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> Starting IPU A-MMU configurations... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> IPU A-MMU configuration completed. <<<---

Cortex_M4_IPU1_C0: GEL Output: ------------------------------------------------------------------------------------------

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR and DPLL configuration Based on Package selection pin status(Sysboot[7]) <<<---

Cortex_M4_IPU1_C0: GEL Output: ------------------------------------------------------------------------------------------

Cortex_M4_IPU1_C0: GEL Output: --->>> 15x15 Package Detected(SYSBOOT[7]=0)... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Clock Configuration for OPPNOM in progress... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> CORE DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> CORE DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> PER DPLL OPP 0 clock config in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> PER DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> DSP_GMAC DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> DSP_GMAC DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> EVE_VID_DSP DPLL OPP 0 clock config is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> EVE_VID_DSP_DPLL OPP 0 is DONE!

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Clock Configuration for OPP 0 is DONE! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Configuration for all modules in progress... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> PRCM Configuration for all modules is DONE! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR3 initialization starts (TI 15x15 EVM)... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR3 Initialization is in progress ... <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR DPLL clock config for 532MHz is in progress...

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR DPLL clock config for 532MHz is in DONE!

Cortex_M4_IPU1_C0: GEL Output: Launch full leveling

Cortex_M4_IPU1_C0: GEL Output: Updating slave ratios in PHY_STATUSx registers

Cortex_M4_IPU1_C0: GEL Output: as per HW leveling output

Cortex_M4_IPU1_C0: GEL Output: HW leveling is now disabled. Using slave ratios from

Cortex_M4_IPU1_C0: GEL Output: PHY_STATUSx registers

Cortex_M4_IPU1_C0: GEL Output: --->>> DDR3 532MHz Initialization is DONE! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Target Connect Sequence DONE !!!!! <<<---

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: GEL Output: For STM based tracing on TI EVMs,

Cortex_M4_IPU1_C0: GEL Output: run 'TDA3x EVM I2C EXPANDER CONTROL -> Enable_Trace_Pins()' function from Scripts menu on M4/CS_DAP_DebugSS

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: GEL Output: Core Reset has occurred.

Cortex_M4_IPU1_C0: File Loader: Verification failed: Values at address 0x83500128 do not match Please verify target memory and memory map.

Cortex_M4_IPU1_C0: GEL: File: E:\ti\PROCESSOR_SDK_RADAR_03_08_00_00\vision_sdk\binaries_2243ES1.0-TDA3x\apps\tda3xx_evm_bios_radar\sbl\qspi_flash_writer\tda3xx-ar12-booster\qspi_flash_writer_ipu1_0_release.xem4: a data verification error occurred, file load failed.

3.Error 0x83500128 is a DDR address. After initializing DDR (CCS - Scripts - DDR Memory Config - TDAxx_DDR3_532MHz_Config), the following error occurs:

>> DDR3 532MHz Initialization is DONE! <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End GMAC_SW MDIO Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Begin GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End GMAC_SW RGMII0 Pad Configuration <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End All Pad Configuration for RGMII usage on EVM Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx End All Pad Configuration for Vision Platform <<<---

Cortex_M4_IPU1_C0: GEL Output: --->>> TDA3xx Target Connect Sequence DONE !!!!! <<<---

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: GEL Output: For STM based tracing on TI EVMs,

Cortex_M4_IPU1_C0: GEL Output: run 'TDA3x EVM I2C EXPANDER CONTROL -> Enable_Trace_Pins()' function from Scripts menu on M4/CS_DAP_DebugSS

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: GEL Output: Core Reset has occurred.

Cortex_M4_IPU1_C0: File Loader: Verification failed: Values at address 0x83500128 do not match Please verify target memory and memory map.

Cortex_M4_IPU1_C0: GEL: File: E:\ti\PROCESSOR_SDK_RADAR_03_08_00_00\vision_sdk\binaries_2243ES1.0-TDA3x\apps\tda3xx_evm_bios_radar\sbl\qspi_flash_writer\tda3xx-ar12-booster\qspi_flash_writer_ipu1_0_release.xem4: a data verification error occurred, file load failed.

4.If you adjust different dip switch modes (visionsdk_userguide_tda3XX. PDF -- 3.4 Boot Mode), the following errors also occur:

The error log is as follows:

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: GEL Output: For STM based tracing on TI EVMs,

Cortex_M4_IPU1_C0: GEL Output: run 'TDA3x EVM I2C EXPANDER CONTROL -> Enable_Trace_Pins()' function from Scripts menu on M4/CS_DAP_DebugSS

Cortex_M4_IPU1_C0: GEL Output: !!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

Cortex_M4_IPU1_C0: GEL Output: --->>> A device reset occurred <<<---

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx PG3.0 device detected =========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx GP Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ========= TDA3xx 15x15 Device detected ===========

Cortex_M4_IPU1_C0: GEL Output: ==================================================

Cortex_M4_IPU1_C0: GEL Output: Core Reset has occurred.

Cortex_M4_IPU1_C0: Can't Run Target CPU: (Error -1268 @ 0x1090001) Device is locked up in Hard Fault or in NMI. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.2.0.00002)