Other Parts Discussed in Thread: SYSBIOS

Situation:

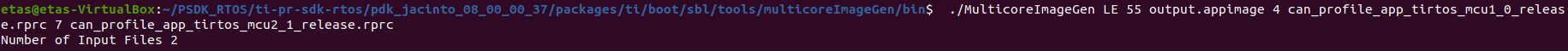

I have made an SD card according to the document and start the app of mcu1_0 from the SD card successfully . However ,I can't start other kernels' app, such as mcu1_1,mcu2_0,mcu2-1,etc from SD card.

Question:

1.Does every kernel need an SBL file?

2.Is sbl_mmcsd_img_mcu1_0_release.tiimage only for mcu1_0?

3.How to load the app of mcu1_1,mcu2_0,mcu2-1,etc from SD card?