Hi,

Could you please help explain below CSNR configuration in pdk_C6678_1_1_2_6\packages\ti\platform\evmc6678l\platform_lib\src\evmc66x_spi.c. It seems that CS1 is configured,which contradictory with cs==0.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

Could you please help explain below CSNR configuration in pdk_C6678_1_1_2_6\packages\ti\platform\evmc6678l\platform_lib\src\evmc66x_spi.c. It seems that CS1 is configured,which contradictory with cs==0.

Hi Nancy,

It seems that CS1 is configured,which contradictory with cs==0.

Let me explain this part,

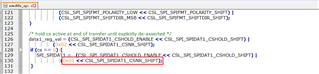

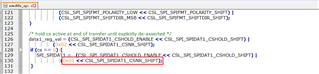

/* hold cs active at end of transfer until explicitly de-asserted */

data1_reg_val = (CSL_SPI_SPIDAT1_CSHOLD_ENABLE << CSL_SPI_SPIDAT1_CSHOLD_SHIFT) |

(0x02 << CSL_SPI_SPIDAT1_CSNR_SHIFT);

if (cs == 0) {

SPI_SPIDAT1 = (CSL_SPI_SPIDAT1_CSHOLD_ENABLE << CSL_SPI_SPIDAT1_CSHOLD_SHIFT) |

(0x02 << CSL_SPI_SPIDAT1_CSNR_SHIFT);

// (CSL_SPI_SPIDAT1_CSHOLD_ENABLE << CSL_SPI_SPIDAT1_CSHOLD_SHIFT) = 1000 0000

// (0x02 << CSL_SPI_SPIDAT1_CSNR_SHIFT) = 0x2 0000

//SO SPI_DAT1 = 0x1002 0000

}

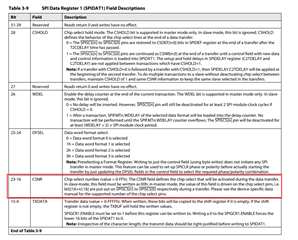

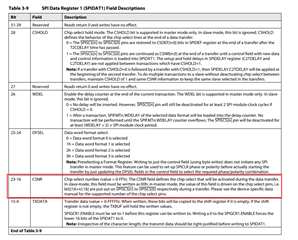

According to SPI user guide, on page 39.

In "SPI_SPIDAT1" in source code,

Here we need to confirm CSNR is pointing to CS0 and not CS1. For that we need C6678 Datasheet, in page 30. It has been mentioned the Chip select number for CS0 is "0x10", which confirms CSNR pointing to CS0.

Thanks,

Rajarajan