Hi TI,

I would like to know why this dts node has two clocks? which clock is truely using? could somebody explain it to me? thanks

a72_0: a72@0 {

compatible = "ti,am654-rproc";

reg = <0x0 0x00a90000 0x0 0x10>;

power-domains = <&k3_pds 61 TI_SCI_PD_EXCLUSIVE>,

<&k3_pds 202 TI_SCI_PD_EXCLUSIVE>;

resets = <&k3_reset 202 0>;

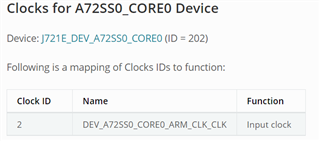

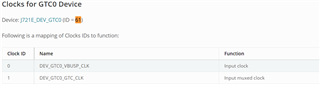

clocks = <&k3_clks 61 1>;

assigned-clocks = <&k3_clks 202 2>, <&k3_clks 61 1>;

assigned-clock-rates = <2000000000>, <200000000>;

ti,sci = <&dmsc>;

ti,sci-proc-id = <32>;

ti,sci-host-id = <10>;

u-boot,dm-spl;

};