Part Number: TMDS243GPEVM

Hi All,

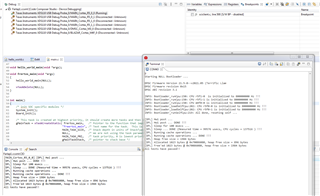

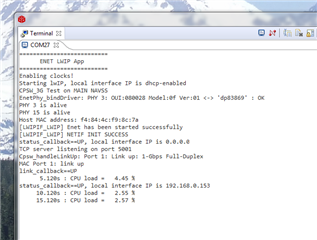

While trying to run the example "enet_lwip_cpsw_am243x-evm_r5fss0-0_freertos_ti-arm-clang" I have encountered the following problem:

CCS = 10.4

SDK = mcu_plus_sdk_am243x_08_01_00_36

The example project compiles and links without problem.

Target configuration (.ccxml) runs without problem.

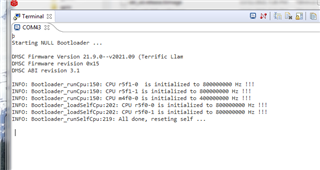

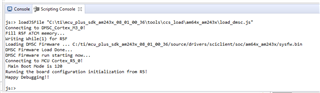

Connection to M3 (DMSC) processor looks ok. Console output follows:

DMSC_Cortex_M3_0: GEL Output: This GEL is currently only supported for use from the Cortex-M3 inside the DMSC.

DMSC_Cortex_M3_0: GEL Output: Do not run this GEL from any other CPU on the SoC.

DMSC_Cortex_M3_0: GEL Output: This script sets the first address translation region to [0x8000_0000, 0x0000_0000].

DMSC_Cortex_M3_0: GEL Output: It also sets the second address translation region to [0x6000_0000, 0x4000_0000].

DMSC_Cortex_M3_0: GEL Output: This is consistent with the SoC DV assumptions.

DMSC_Cortex_M3_0: GEL Output: Configuring ATCM for the R5Fs

DMSC_Cortex_M3_0: GEL Output: ATCM Configured.

DMSC_Cortex_M3_0: GEL Output: R5F Halt bits set.

DMSC_Cortex_M3_0: GEL Output: Configuring bootvectors

DMSC_Cortex_M3_0: GEL Output: Bootvectors configured.

DMSC_Cortex_M3_0: GEL Output: Programming all PLLs.

DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 0 (Main PLL)

DMSC_Cortex_M3_0: GEL Output: Main PLL 0 (Main PLL) Set.

DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 1 (Peripheral 0 PLL)

DMSC_Cortex_M3_0: GEL Output: Main PLL 1 (Peripheral 0 PLL) Set.

DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 2 (Peripheral 1 PLL)

DMSC_Cortex_M3_0: GEL Output: Main PLL 2 (Peripheral 1 PLL) Set.

DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 8 (ARM0 PLL)

DMSC_Cortex_M3_0: GEL Output: Main PLL 8 (ARM0 PLL) Set.

DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 12 (DDR PLL)

DMSC_Cortex_M3_0: GEL Output: Main PLL 12 (DDR PLL) Set.

DMSC_Cortex_M3_0: GEL Output: Programming Main PLL 14 (Main Domain Pulsar) PLL)

DMSC_Cortex_M3_0: GEL Output: Main PLL 14 (Main Domain Pulsar PLL) Set.

DMSC_Cortex_M3_0: GEL Output: Programming MCU PLL 0 (MCU PLL)

DMSC_Cortex_M3_0: GEL Output: MCU PLL 0 (MCU PLL) Set.

DMSC_Cortex_M3_0: GEL Output: All PLLs programmed.

DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains in progress...

DMSC_Cortex_M3_0: GEL Output: Powering up MAIN domain peripherals...

DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DMSC

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_TEST

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN_PBIST

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_4B

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMMC_8B

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_USB

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ADC

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_DEBUGSS

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_GPMC

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_CFG

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_EMIF_DATA

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_0

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCAN_1

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SA2UL

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_SERDES_0

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PCIE_0

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL done.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_0

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_0_R5_1

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_0

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_0 done.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_0

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_1_R5_1

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_PULSAR_PBIST_1

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_PULSAR_1 done.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_0

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_0 done.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_ICSSG_1

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_ICSSG_1 done.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_CPSW3G

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_CPSW done.

DMSC_Cortex_M3_0: GEL Output: Powering up all MAIN domain peripherals done.

DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals.

DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_TEST

DMSC_Cortex_M3_0: GEL Output: Power domain and module state changed successfully.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MAIN2MCU

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_MCU2MAIN

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up GP_CORE_CTL_MCU done.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F.

DMSC_Cortex_M3_0: GEL Output: Powering up LPSC_M4F

DMSC_Cortex_M3_0: GEL Output: No change needed.

DMSC_Cortex_M3_0: GEL Output: Powering up PD_M4F done.

DMSC_Cortex_M3_0: GEL Output: Powering up MCU Domain peripherals done.

DMSC_Cortex_M3_0: GEL Output: Powering up all PSC power domains done!

DMSC_Cortex_M3_0: GEL Output:

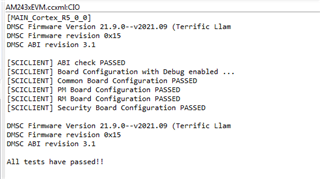

Connection to R5_0_0 looks ok:

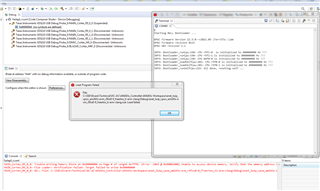

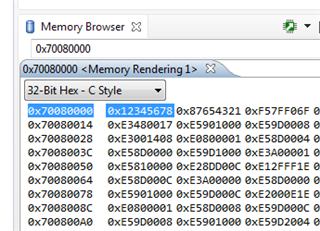

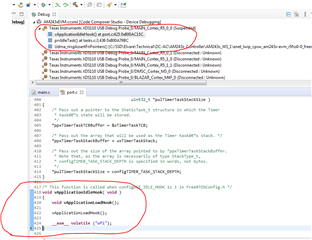

Executing script "AM24_DDR_Initialization_ECC_Disabled"

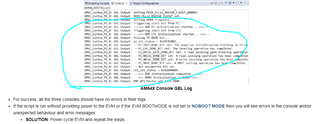

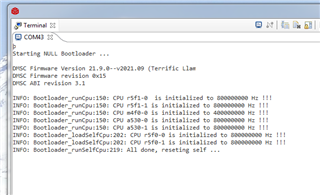

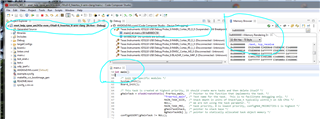

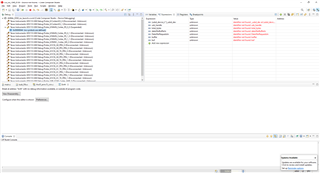

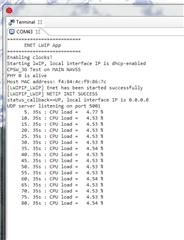

Here is a screen shot of console showing where the script stalls:

The above is from a PC with Win7 OS.

I have tried the same sequence on a Win10 PC with the same results.

Thanks in advance,

Joel