Part Number: PROCESSOR-SDK-AM64X

Hi,

according to https://software-dl.ti.com/processor-sdk-linux-rt/esd/AM64X/07_03_00_02/exports/docs/linux/Foundational_Components/Kernel/Kernel_Drivers/Network/CPSW3g.html#common-platform-time-sync-cpts-module the SDK provides a PTP hardware clock (phc) in the root fs /dev/ptpN with the following capabilities:

Basic clock operations - Set time - Get time - Shift the clock by a given offset atomically - Adjust clock frequency

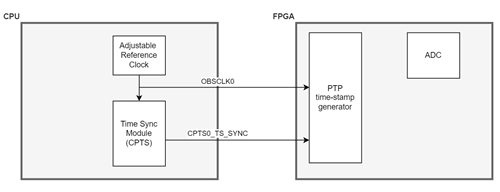

I need to synchronize an external PTP clock (implemented in an FPGA) to that phc clock and I'm wondering if it is possible to output this adjustable clock to the obsclk pin so that it could be used as reference clock in the FPGA

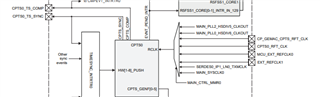

How is the adjustment of the clock frequency implemented? Fractional PLL or just by skipping or adding clock periods? The CPTS module can be clocked from different clock sources,

which source is used?

Can somebody give me some details how this phc is implemented?

Thank you for your reply!

Best regards

Reto