Part Number: DRA821U

Dear support,

For the following problem, we need your support. Thank you in advance!

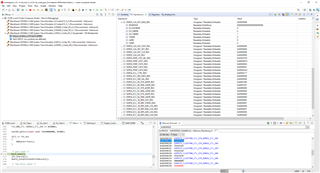

1 ddr ecc address register - ddrss_ecc_ri_str_addr_reg and ddrss_ecc_ri_end_addr_reg

in the pku package, the below formula will be caculated and then assign to ddrss_ecc_ri_str_addr_reg and ddrss_ecc_ri_end_addr_reg

ddrss_ecc_ri_str/end_addr_reg = ((actual_addr - 0x8000 0000) >> 16) & 0x7 FFFF

So, if I want to protect range 0x9000 0000 ~ 0x9000 FFFF, how to configure ddrss_ecc_ri_str_addr_reg and ddrss_ecc_ri_end_addr_reg

ddrss_ecc_ri_str_addr_reg = 0x9000 0000, ddrss_ecc_ri_end_addr_reg = 0x9001 0000?

The protected address resolution is 64KB?

2 I use the error injection interface - DDRSecErrTest, the error injection address is 0x9000 0100,

In the DDRGetTranslatedAddress api. it translate 0x9000 0100 as 0x9200 0100, and then write the corrupt data in 0x9200 0100.

Can you give us a simple description about the principle of this translation?

Is there any DDR layout when DDR ECC is enabled.

3 how to translate the address to the mapped the DDR address 0x8000 0000 ~ 0x9FFF FFFF(512MB)?

we inject one bit ecc error in 0x9000 0100, but we got the DDRSS_ECC_1B_ERR_ADR_LOG_REG as 0x0080 0008