Other Parts Discussed in Thread: DS90UB960-Q1

Hello TI support.

We are using TDA4VM and related board.

In that board, there is a Deserializer DS90UB960-Q1. We want to know:

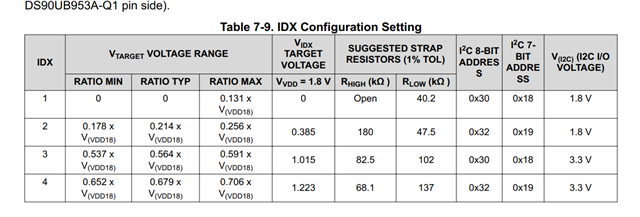

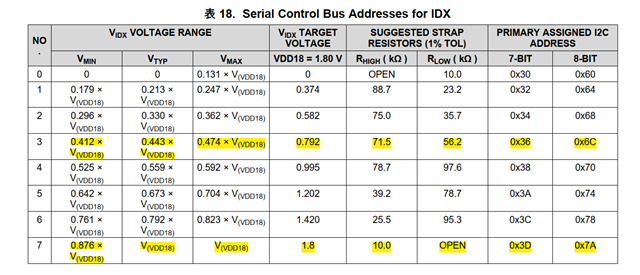

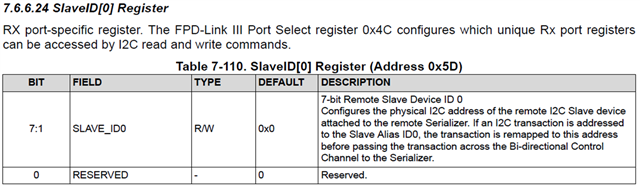

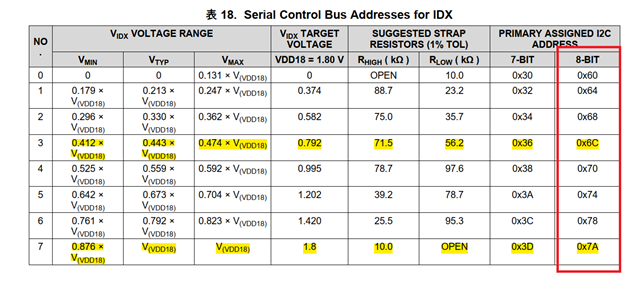

1) what is the device address(I2C address) of DS90UB960-Q1 in TDA4VM?

2) how can we know it is using 7-bit or 8-bit address?

Regards,

Li