Part Number: TDA4VM

As per the TDA4VM TRM, the ARM Corext-A72 Subsystem used by the TDA4VM supports "Advanced Single Instruction Multiple Data (SIMD) and floating point extension (Arm Neon)".

- Please refer to this page that points to the ARM Architecture Reference Manual that gives full instruction set details.

- Notes on using GCC with Neon, are at ARM NEON Intrinsics - Using the GNU Compiler Collection (GCC)

- The ARM ID_AA64PFR0_EL1 register will specify whether the NEON feature is enabled or not, See (Arm Armv8-A Architecture Registers).

A view from CCS on PSDK QNX 7.3 on J721E EVM is shown below indicating support of Advanced SIMD (Neon)

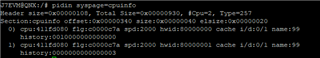

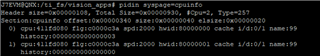

During boot up the QNX BSP will read ARM register ID_AA64PFR0_EL1 to determine if NEON is supported by the underlying platform. This status of the BSP check can in turn be read from the QNX command line, using the below command, documented at - cpuinfo (qnx.com), see ARM_CPU_FLAG_NEON (0x40).

pidin syspage=cpuinfo

Example of QNX HLOS viewing NEON as enabled

Example of QNX HLOS view NEON as disabled

If QNX HLOS is viewing NEON as disabled on Jacinto7 family of devices, (TDA4x, J7x), this is incorrect, and the following file in the BSP should be checked to ensure that bit masks are set correctly.

BSP File: ./src/hardware/startup/lib/aarch64/init_cpuinfo.c

The below macro definitions in this file should be set as below to check for NEON support:

#define AA64PFR0_SIMD(x) ((((x) >> 20) & 0xfUL) != 0xfUL)

#define AA64PFR0_FP(x) ((((x) >> 16) & 0xfUL) != 0xfUL)

If the bitmask are using 0xFF, NEON may be falsely viewed as not supported.

To address, this an updated BSP can be downloaded, or make the code change as hi-lited above, rebuild the BSP, and check via QNX command line to ensure the ARM_CPU_FLAG_NEON (0x40) is set correctly.