Hi experts,

My customer wants to do an AM5726 PCIe RX jitter tolerance test.

They have been able to perform tests other than PCIe's RX jitter tolerance test without any problems. But they can't just do RX jitter tolerance test.

I have the following questions about this:

- Is Sitara's PCIe physical layer designed to properly enter loopback mode when a standardized training pattern arrives at Sitara's PCIe physical layer?

- If Sitara does not go into loopback mode due to the training pattern, can they force Sitara into loopback mode with a register etc.?

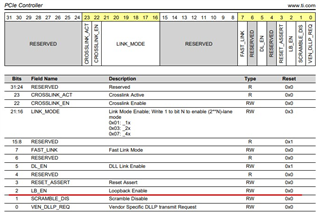

- I found the following bit in TRM, what does this bit do?

Detail:

They used the PCIe sample program on their board to run the AM5726 as a root complex. When they are connected with an oscilloscope via CLB (Compliance Load Board), compliance patterns are output and they can evaluate eye diagrams and reference clocks.

After that, they needed to put Sitara in loopback mode to do the RX Jitter Tolerance exam, and tried to put Sitara in loopback mode by externally giving a training sequence through the sequence editor, but they couldn't.

Best regards,

Sasaki