Part Number: DRA829V

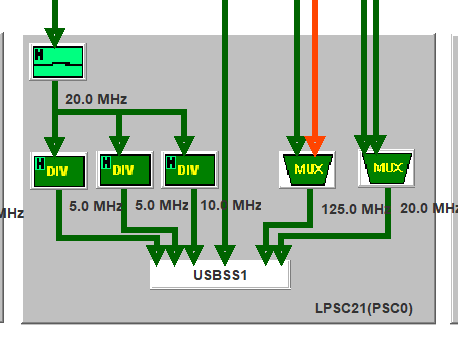

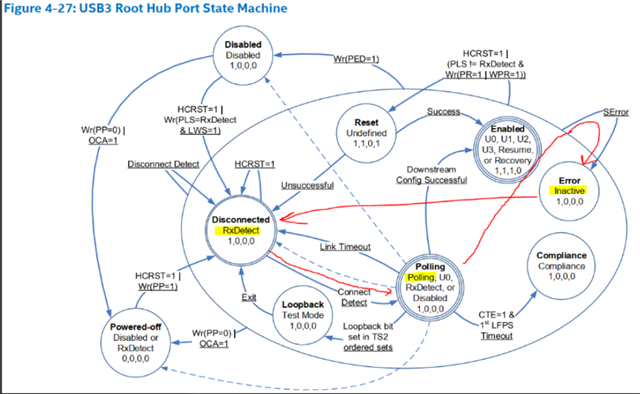

I am having trouble getting the USB3.0 host controller to connect with a device on a type C connector on USBSS1. The device will connect at HS but not SS. I am verifying that the clocks are set up correctly.

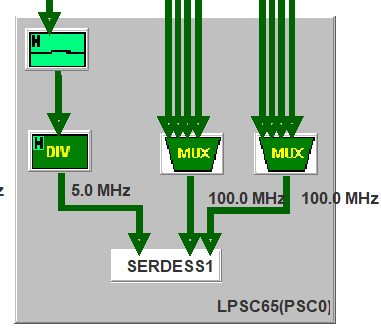

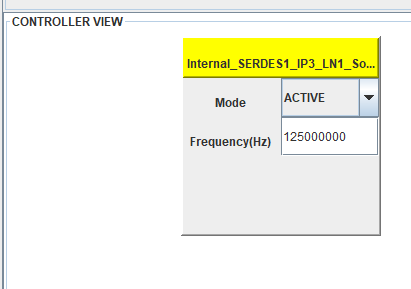

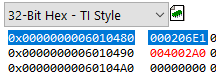

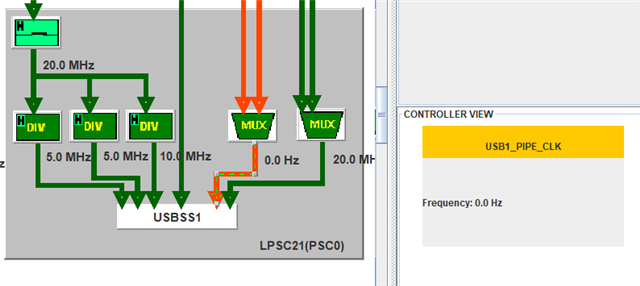

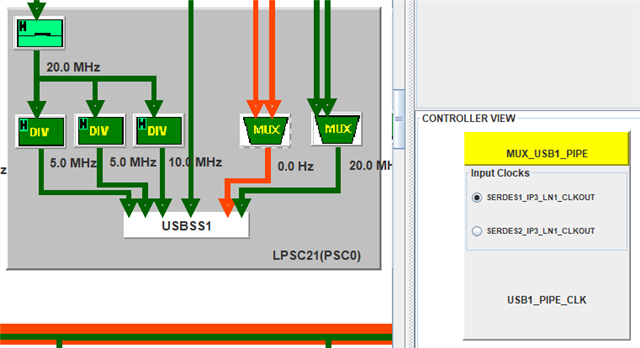

The Clock Tree Tool shows a clock called USB1_PIPE_CLK that is not enabled (red) but there is no documentation for this that I could find in the TRM. I am using SERDES1.

The Mux shows it is set up to choose the SERDES1_IP_LN1_CLKOUT

I will have more things to check on this thread but I want to verify the clocks are set up correctly first.

The CTT does not show ACLK either.

Where is USBSS1 ACLK in CTT?

What is USB1_PIPE_CLK in CTT?