Other Parts Discussed in Thread: SYSCONFIG

Do I need to put a delay between bytes in a SPI multibyte transfer?

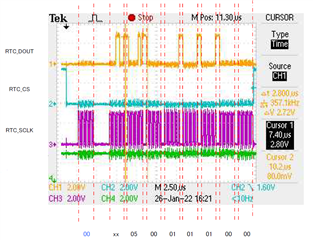

When I performed multi-byte transfer between AM3352 and DS3234 of RTC IC, the interval between bytes was about 500ns, and a transfer error started to occur. The DS3234 is operated with a 4MHz clock.

I have confirmed from the oscilloscope waveform that the correct data is being transmitted from the DS3234, but the value stored in the receive register of the AM3352 is incorrect.

By setting the interval between bytes to 1us or more, transfer errors no longer occur, but I would like to make the delay between bytes a valid number rather than "somehow".

Best Regard.