Dear Champs,

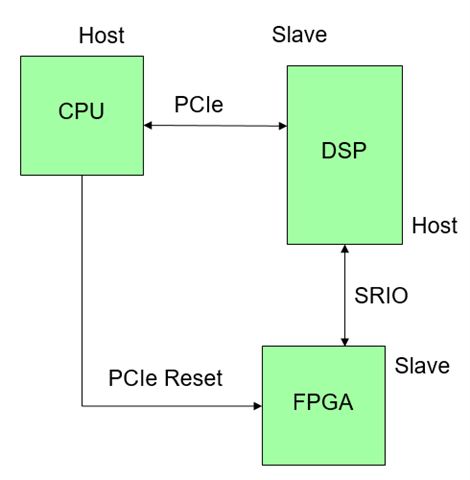

My customer would like to check their boot-up order if there is no timing issue to establish SRIO connection between DSP and FPGA, and their system configuration is as below.

In this case, FPGA which is SRIO slave device is boot-up after DSP which is SRIO host boot-up. e.g. DSP -> FPGA.

Could you please check if there is any SRIO connection issue in this case?

Thanks and Best Regards,

SI.