Hi:

I use sdk8.1,in ti-processor-sdk-rtos-j721e-evm-08_01_00_11/pdk_jacinto_08_01_00_33,

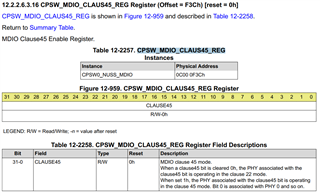

we board use 88q2112 phy for cpsw_9G,

Manually set 100BASE-T1, read the phy state is linked, and then read the mdio linked register on the TDA4 side is always link down, what's going on?

pdk_jacinto_08_01_00_33\packages\ti\csl\src\ip\mdio\V5\priv\csl_mdio.c

CSL_MDIO_isPhyAlive

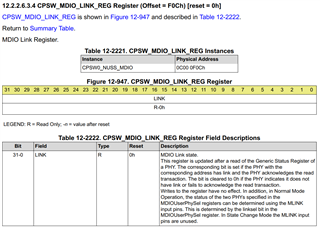

CSL_FEXTR (hMdioRegs->LINK_REG, phyAddr, phyAddr);

88q2112 phy reg read status linked,but read soc mdio linked reg is 0:

CSL_MDIO_isPhyAlive return 0

Thanks,

Regards,

Jie