Hi team,

Here's an issue from the customer may need your help:

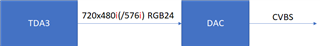

In the spec of TDA3, here're two types of image output: [9.1.1.1 Display Subsystem Parallel Interface], [9.1.1.2 Display Subsystem TV Output].

The customer has designed a PCBA, the output of this PCBA is given in 720p RGB24 image format via [9.1.1.1 Display Subsystem Parallel Interface]. To the next IC, which is a high-definition DAC that can be used for normal output-class high-definition images:

With the same hardware design, can 720x480i (or 720*576i) be given through the [9.1.1.1 Display Subsystem Parallel Interface] to the later IC for the DAC to be scaled? If the hardware design is OK, can this be used in the SDK software firmware portion as well?

Could you help check this case? Thanks.

Best Regards,

Cherry