Part Number: TDA4VM

Hi Expert.

Thanks for your previouse answer.

about TIFS,i have another new questions:

1.tifs.bin is loaded from external media into wakeup domamin internal SRAM.

-->who can modify tifs? only TI or the user can modify it?if user can moidfy it,where i can get more information about this?

2.if user can modify tifs.bin and tifs.bin is loaed into wakup domain(M3 core) internal SRAM.

-->what is the size of this internal SRAM? where i can get this informaiton? i did not find wakup domain internal ROM/RAM size information from datasheet.

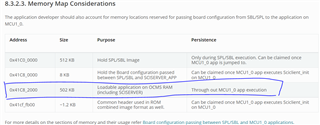

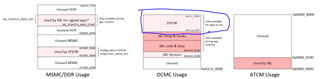

3.see following picture blue box,address 41C8_0000~41CC_0000 is used by SBL,but from 41C8_2000,it is the location of mcu_1_0 app which shall be loaded by SBL

-->conflicting usage? or SYSFW area(41C8_2000~41CC_0000) is released then mcu_1_0 app is loaded?