I would like to run YoloP (https://github.com/hustvl/YOLOP) on TI edge.

When I try to convert a yoloP onnx into TI edge format, I get these errors:-

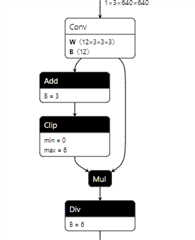

ONNX operator Div is not suported now.. By passing

ONNX operator Div is not suported now.. By passing

ONNX operator ScatterND is not suported now.. By passing

ONNX operator ScatterND is not suported now.. By passing

ONNX operator ScatterND is not suported now.. By passing

ONNX operator ScatterND is not suported now.. By passing

ONNX operator ScatterND is not suported now.. By passing

ONNX operator ScatterND is not suported now.. By passing

Can someone help me resolve these and anything else needed to run YoloP in TI edge?

Thanks!