Hi Support Team,

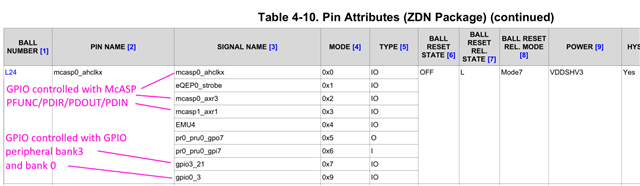

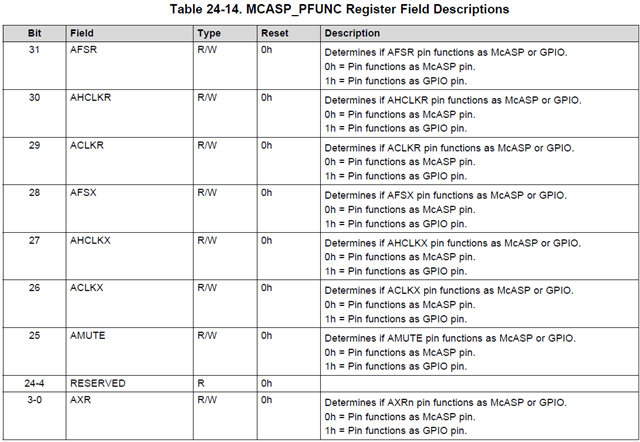

In the MCASP_PFUNC register, it seems that it is possible to set

whether Pin fuciton is McASP or GPIO as shown below,

but how is this setting related to the mode setting of Control Module register

setting CTRL_CONF_each pin name?

For example, if I want to use pin MCASP0_AXR1 as GPIO,

do I need to set B[3:0]=0x7 mode7 in CTRL_CONF_MCASP0_AXR1 and B[3:0]=0x1 in MCASP_PFUNC?

Or if I set B[3:0]=0x7 in CTRL_CONF_MCASP0_AXR1,

will this setting take priority and the device will function as a GPIO regardless of the MCASP_PFUNC setting?

Best regards,

Kanae